# Design Automation and QoS Requirements Preservation for Multiprocessor Embedded Systems

by Md. Al Maruf

A thesis submitted to the School of Graduate and Postdoctoral Studies in partial fulfillment of the requirements for the degree of

Master of Applied Science in Electrical and Computer Engineering

Faculty of Engineering and Applied Science Ontario Tech University, Canada

July 2019

©Md. Al Maruf, 2019

## THESIS EXAMINATION INFORMATION

## Submitted by: Md Al Maruf

## Master of Applied Science in Electrical and Computer Engineering

Thesis title: Design Automation and QoS Requirements Preservation for Multiprocessor Embedded Systems

An oral defense of this thesis took place on June 12, 2019 in front of the following examining committee:

## **Examining Committee:**

| Chair of Examining Committee | Dr. Walid Morsi Ibrahim |

|------------------------------|-------------------------|

| Research Supervisor          | Dr. Akramul Azim        |

| Examining Committee Member   | Dr. Qusay Mahmoud       |

| Thesis Examiner              | Dr. Patrick Hung        |

The above committee determined that the thesis is acceptable in form and content and that a satisfactory knowledge of the field covered by the thesis was demonstrated by the candidate during an oral examination. A signed copy of the Certificate of Approval is available from the School of Graduate and Postdoctoral Studies.

# ABSTRACT

The number of processors is increasing in embedded systems but the usefulness of parallel computation is not better leveraged due to the inflexibility of design and implementation for multiprocessor embedded system applications. A higher level abstraction (i.e., a parallel programming framework) can ease the programmers to define parallelism for tasks in an application, but designers still face the complexity of mapping high-level requirements to the syntax and semantics of a parallel programming interface. Nevertheless, embedded system applications execute various periodic tasks that are carried out repeatedly within a certain time interval. Each task is characterized by its deadline where it is expected to perform a function producing a correct result within a specified amount of time. These tasks may be able to run in parallel to utilize the system efficiently. Moreover, embedded systems often interact with dynamic environments requiring not only to meet deadlines of tasks but also to achieve a certain level of accuracy as the inaccuracy of a task output produces a similar adverse effect like timing violation. Therefore, it requires an automated design process to map the tasks to lower level and a monitoring framework to meet the high-level requirements of embedded system applications.

This thesis presents a parallel loop-based task construct to automate the design process of embedded applications from Architecture Analysis and Design Language (AADL) models and demonstrates how to preserve the requirements at lower-levels. AADL is practiced to model the software and hardware architecture of embedded systems. Since most of today's embedded systems either belong to soft real-time systems (i.e., stream processing systems) or weakly-hard real-time systems (e.g., control systems), we adopt a new task scheduling approach in a well-known parallel programming interface called OpenMP for increasing determinism in soft real-time system (RTS) applications. Moreover, we propose a calibration framework to increase the robustness of weakly-hard real-time system applications that rely on time-driven scheduling approaches such as rate monotonic (RM) scheduling. In this thesis, determinism and robustness are the way of measuring the quality of service (QoS) requirements of tasks. For increasing the robustness of weakly-hard real-time systems, the calibration framework is used by which the system component's output accuracy can be monitored and compared with a calibration standard. The calibration standard is derived from a representative component's output with known high accuracy. As an example, we analyze the accuracy of a component that performs dynamic voltage and frequency scaling (DVFS) and explains the associated timing effects in terms of task schedulability.

To illustrate the applicability of our mechanism, the experimental analysis incorporates a design automation process for mapping tasks to parallel programming framework in soft RTSs, a calibration framework for monitoring task output in weakly-hard RTSs. To understand the calibration framework, a software-based monitoring approach is shown for a resistive voltage divider as a case study. Therefore, we use a cost estimation model to demonstrate the efficiency of the automation process and map tasks over multiple processor cores using OpenMP. To ensure meeting high-level requirements of embedded system applications, we analyze the existing OpenMP scheduling mechanisms and propose a layer of adaptation. We show that our proposed adaptation layer facilitates a tighter execution time bound for time-sensitive tasks or a better throughput for tasks that require higher QoS. Thus, the proposed design automation framework is applicable for a variety of applications with different QoS requirements preserved at the lower level. To monitor the QoS of task output, we perform experiments on LITMUS<sup>RT</sup> kernel to demonstrate the need and applicability of our calibration framework in the domain of embedded systems. The experimental results illustrate that the proposed approach yields more predictability and show better performance for preserving QoS requirements of tasks.

# AUTHORS DECLARATION

I hereby declare that this thesis consists of original work of which I have authored. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize the Ontario Tech University to lend this thesis to other institutions or individuals for the purpose of scholarly research. I further authorize Ontario Tech University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. I understand that my thesis will be made electronically available to the public.

Md. Al Maruf

# STATEMENT OF CONTRIBUTIONS

The contributions of my work are listed as follows:

a) We present a design automation process for mapping and preserving high-level requirements in soft and weakly-hard RTSs. We propose a loop-based task construct to map periodic tasks into a parallel programming framework (i.e., OpenMP) in soft RTSs where the requirements are extracted from AADL model specifications. These requirements are considered as high QoS requirements or low QoS requirements.

b) In the case of weakly-hard RTSs, we present a calibration framework using LITMUS<sup>RT</sup> which monitors the task requirements that are reliant on the accuracy of the system components. Moreover, it will guide to take action after comparing the output with standards to ensure the expected component's output accuracy.

c) In another work, we present a case study of a resistive voltage divider for a softwarebased auto calibration framework in the absence of a proper calibration standard. It examines the outputs of the voltage divider to find anomalies and notifies the system when the output goes out from the expected result.

A Part of the above the contributions has already been published as:

Md. Al Maruf, and Akramul Azim. "Software-based Monitoring for Calibration of Measurement Units in Real-time Systems." IECON 2018-44th Annual Conference of the IEEE Industrial Electronics Society. IEEE, 2018, USA.

# ACKNOWLEDGEMENTS

I would first like to express my heartiest gratitude to the Almighty Allah for giving me the strength to finalize this thesis.

I want to express the most profound appreciation to my supervisor Dr. Akramul Azim, Assistant professor, UOIT for his useful comments, remarks and engagement through the learning process of this master thesis. He provided me invaluable guidance, support and immense inspiration towards the completion of this thesis. The door to Dr. Akramul Azim office was always open for me, and I always ran toward his office whenever I faced any problem in my research. He consistently allowed me to work in my own interest and provided me the right direction when it was required. Thanks for believing in me and helping me in all aspects of my thesis work.

Furthermore, I would like to thank all of my RTEMSOFT research group members who have supported me throughout the entire process, both by helpful criticism sharing thoughts to improve my work. Many thanks to the members of the Software System Research Lab who contributed to the friendly atmosphere in my workplace. I also appreciate the support of all my friends, colleagues, and relatives who always motivated and encouraged me through this journey. I want to acknowledge the helpful assistance and instructions from the respected faculty members and staffs of Ontario Tech University.

Finally, I must express my very profound gratitude to my family, especially my beloved mother Mahfuza Begum, my father Motalleb Hossain, my sister Khairun Nesa, and my brother Naim Ali for their unconditional support and continuous encouragement throughout my years of study. This accomplishment would not have been possible without them. Thank you.

# Contents

| A  | bstra | ict     |                                                                                                                                        | i            |

|----|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| A  | UTH   | ORS I   | DECLARATION                                                                                                                            | iii          |

| A  | cknov | wledge  | ments                                                                                                                                  | $\mathbf{v}$ |

| Li | st of | Figur   | es                                                                                                                                     | ix           |

| Li | st of | Tables  | 5                                                                                                                                      | xi           |

| A  | bbre  | viation | IS                                                                                                                                     | xii          |

| 1  | Intr  | oducti  | ion                                                                                                                                    | 1            |

|    | 1.1   | Desigr  | a automation of parallel periodic tasks                                                                                                | 2            |

|    |       | 1.1.1   | Mapping of AADL specifications to a loop-based task construct                                                                          |              |

|    |       | 1.1.2   | Task scheduling                                                                                                                        | 3            |

|    | 1.2   | QoS R   | Requirements preservation                                                                                                              | 3            |

|    |       | 1.2.1   | Requirements adaptation layer                                                                                                          | 4            |

|    |       |         | 1.2.1.1 Satisfying QoS requirements for soft RTSs                                                                                      | 4            |

|    |       |         | 1.2.1.2 Satisfying QoS requirements for weakly-hard RTSs                                                                               | 5            |

|    |       | 1.2.2   | Monitoring task output for calibration                                                                                                 | 7            |

|    | 1.3   | Challe  | enges in requirements preservation                                                                                                     | 8            |

|    |       | 1.3.1   | System-level formal specification                                                                                                      | 8            |

|    |       | 1.3.2   | Embedded software complexity                                                                                                           | 8            |

|    |       | 1.3.3   | Requirements integration                                                                                                               | 9            |

|    |       | 1.3.4   | Selection of a task scheduling approach                                                                                                | 9            |

|    | 1.4   | Thesis  | $s objectives \ldots \ldots$         | 9            |

|    | 1.5   | Contri  | ibutions                                                                                                                               | 10           |

|    | 1.6   | Organ   | ization of the thesis                                                                                                                  | 10           |

| 2  | Lite  | erature | e review                                                                                                                               | 12           |

|    | 2.1   | Introd  | $uction \ldots \ldots$ | 12           |

|    | 2.2   | State   | of the art of design automation and requirements monitoring $\ . \ . \ .$                                                              | 13           |

|    |       | 2.2.1   | Language-based design                                                                                                                  |              |

|    |       | 2.2.2   | Model-based design                                                                                                                     | 13           |

|   |      | 2.2.3  | Implementation a                      | pproaches in a multiprocessor platform                        | 14 |

|---|------|--------|---------------------------------------|---------------------------------------------------------------|----|

|   | 2.3  | Appro  | aches to monitorin                    | g                                                             | 16 |

|   |      | 2.3.1  | Hardware Monito                       | rs                                                            | 17 |

|   |      | 2.3.2  | Software monitor                      | 5                                                             | 17 |

|   |      | 2.3.3  |                                       |                                                               | 17 |

|   | 2.4  | Task s | U C                                   | hes in multiprocessor systems                                 | 18 |

|   |      | 2.4.1  |                                       | aches                                                         | 18 |

|   |      | 2.4.2  | ~                                     | t                                                             |    |

|   |      | 2.4.3  |                                       | task scheduling                                               |    |

|   | 2.5  | Calib  |                                       | embedded systems                                              |    |

|   |      | 2.5.1  |                                       | easurements                                                   |    |

|   |      | 2.5.2  |                                       | ation                                                         |    |

|   |      | 2.5.3  | -                                     |                                                               |    |

|   |      | 2.5.4  |                                       | calibration                                                   |    |

|   |      |        |                                       |                                                               |    |

| 3 | Des  | ign au | $\mathbf{O}$ omation and $\mathbf{Q}$ | S requirements preservation in multiproces-                   |    |

|   | sors | 3      |                                       |                                                               | 28 |

|   | 3.1  | Introd | uction $\ldots$ $\ldots$ $\ldots$     |                                                               | 28 |

|   | 3.2  | Syster | n model and assum                     | nptions                                                       |    |

|   | 3.3  | Desig  |                                       | apping requirements                                           | 32 |

|   |      | 3.3.1  |                                       | pop-based task construct from AADL                            | 32 |

|   |      |        | •                                     | ing AADL components                                           | 32 |

|   |      |        |                                       | specification to $C++$ code conversion $\ldots \ldots \ldots$ | 33 |

|   | 3.4  | Propo  |                                       | oS requirement preservation                                   | 34 |

|   |      | 3.4.1  |                                       | oS requirements in soft RTSs                                  | 34 |

|   |      |        | 3.4.1.1 QoS req                       | uirements evaluation                                          | 36 |

|   |      |        | -                                     | d thread to processor binding approach                        | 36 |

|   |      |        | U                                     | m for requirements adaptation                                 | 36 |

|   |      |        | 3.4.1.4 Adaptat                       | ion constraints                                               | 38 |

|   |      |        | 3.4.1.5 Discussi                      | on                                                            | 39 |

|   |      | 3.4.2  |                                       | oS requirements in weakly-hard RTSs                           |    |

|   |      |        | 3.4.2.1 Necessit                      | y of calibration: A rational example                          | 41 |

|   |      |        | 3.4.2.2 Finding                       | execution time delay for output inaccuracy                    | 44 |

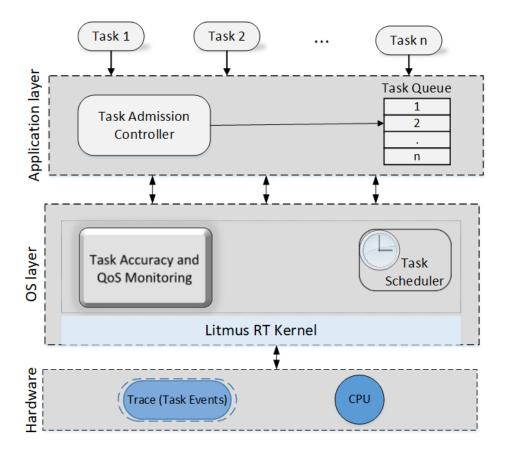

|   |      |        | 3.4.2.3 Propose                       | d calibration framework                                       | 45 |

|   |      |        | 3.4.2.4 The wor                       | king principle of a software-based calibration                | 49 |

|   |      |        | 3.4.2.5 Discussi                      | on                                                            | 56 |

| 4 | Exp  | oerime | tal results and                       | analysis                                                      | 57 |

|   | 4.1  |        |                                       | ·                                                             | 57 |

|   | 4.2  | Analy  | is of design autom                    | ation and requirements preservation in soft RTSs              | 57 |

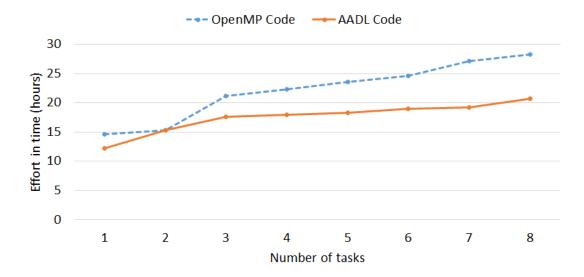

|   |      | 4.2.1  | Importance of des                     | sign automation in writing parallel programs                  | 58 |

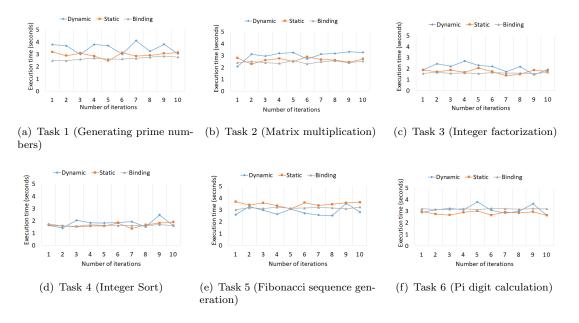

|   |      | 4.2.2  | -                                     | ministic task execution using OpenMP                          | 60 |

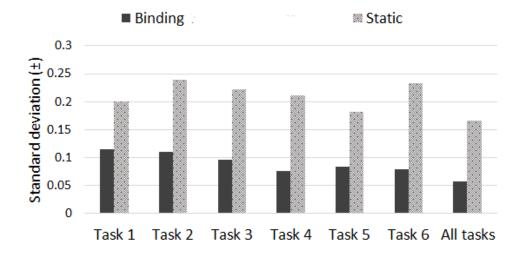

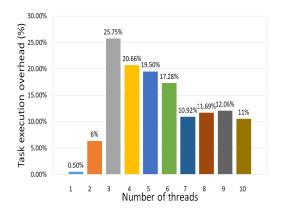

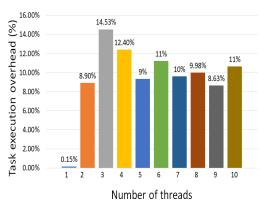

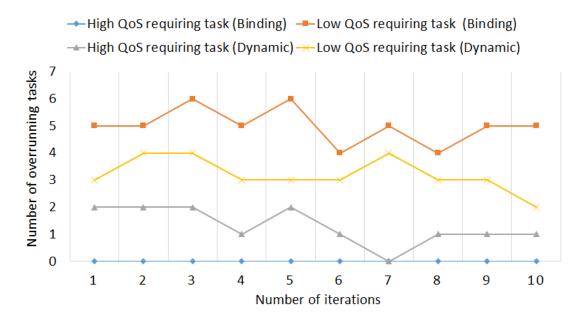

|   |      | 4.2.3  |                                       | s of the proposed binding approach                            | 61 |

|   |      | 4.2.4  | •                                     | rements preservation of the proposed thread to                |    |

|   |      |        | •                                     | approach                                                      | 64 |

|   | 4.3  | Monit  | oring accuracy for                    | requirements preservation in weakly-hard RTSs .               | 65 |

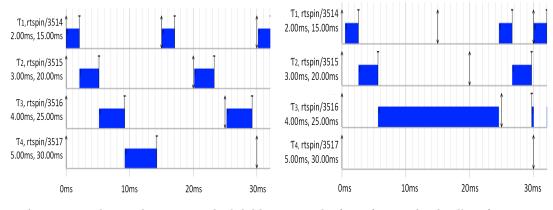

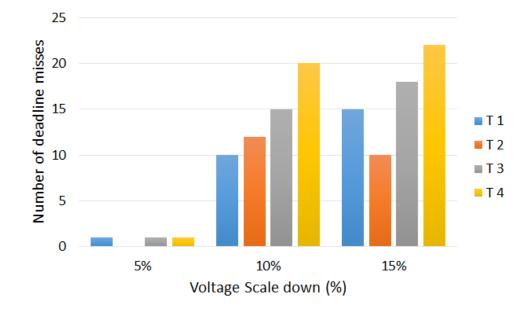

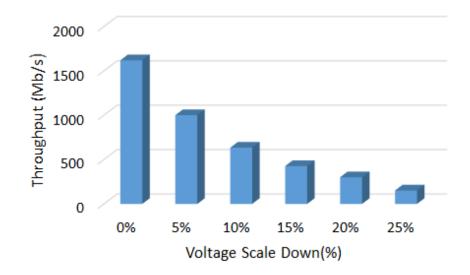

|   |      | 4.3.1  | Analysis of task s                    | chedulability test                                            | 66 |

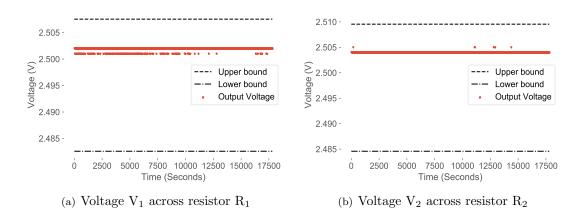

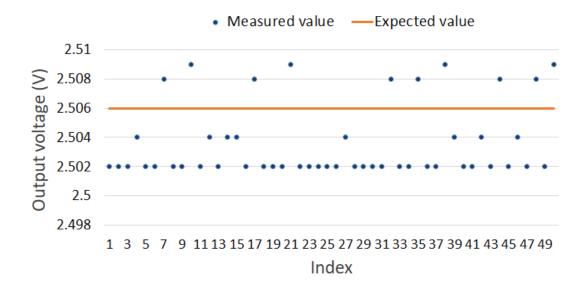

|    | $\begin{array}{c} 4.3.2 \\ 4.3.3 \\ 4.3.4 \end{array}$ | Task output analysis from recorded trace in LITMUSError correction for calibrationAnalysis of software-based calibration in a resistive voltage divider | 67 |

|----|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | Conclusion                                             | n and future work                                                                                                                                       | 73 |

| A  | List of sy                                             | mbols                                                                                                                                                   | 76 |

| Bi | bliography                                             |                                                                                                                                                         | 79 |

# List of Figures

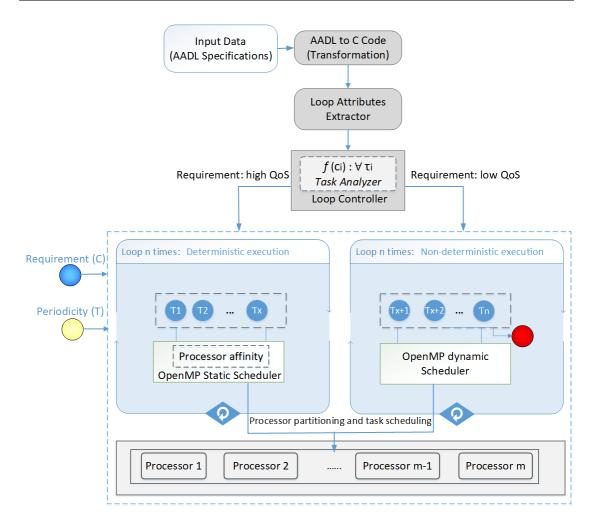

| 1.1               | An abstract view of our design automation and requirements preservation<br>workflow                                                             | 5        |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2               | Execution time changes for different CPU frequencies [1]                                                                                        | 7        |

| 2.1               | Output monitoring in embedded systems                                                                                                           | 16       |

| 2.2               | Partitioned Scheduling [2]                                                                                                                      | 20       |

| 2.3               | Global Scheduling [2]                                                                                                                           | 20       |

| 2.4               | Drift and offset variation from actual measurement value                                                                                        | 26       |

| 3.1               | Details workflow of the proposed approaches                                                                                                     |          |

| 3.2               | AADL model specification to $C++$ Code transformation $\ldots \ldots \ldots$                                                                    |          |

| 3.3               | AADL model specifications                                                                                                                       | 31       |

| 3.4               | System model layered architecture                                                                                                               |          |

| $\frac{3.5}{3.6}$ | A snippet of a generated C/C++ Code from AADL specifications $\dots$ .<br>Proposed design automation framework for requirement-preserving loop- | 33       |

|                   | based task constructs                                                                                                                           |          |

| 3.7               | Thread to processor binding approach                                                                                                            |          |

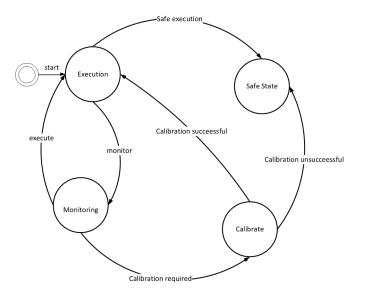

| 3.8               | State machine model for calibration approach                                                                                                    | 40       |

| 3.9               | A calibration framework                                                                                                                         | 42       |

| 3.10              | An example of a deadline miss due to inaccurate voltage output                                                                                  | 44       |

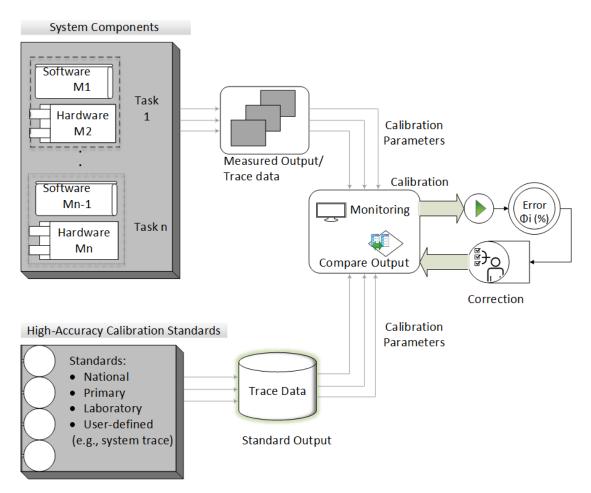

| 3.11              | A calibration framework for monitoring accuracy                                                                                                 | 45       |

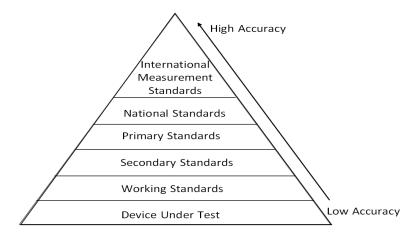

| 3.12              | Types of measurement standards                                                                                                                  | 51       |

| 4.1               | Estimated efforts comparison between a OpenMP parallel program code<br>and an AADL based design Code.                                           | 59       |

| 4.2               | OpenMP task execution time differences among dynamic, static, and the thread to processor binding approaches                                    | 61       |

| 4.3               | Variation of execution times between the static approach and the thread to processor binding approach                                           | 62       |

| 4.4               | Overhead on using the proposed binding approach compared to the dy-<br>namic approach with varying number of threads                            | 63       |

| 4.5               | Number of overrunning tasks in binding (thread to processor) and dy-<br>namic scheduling approach                                               |          |

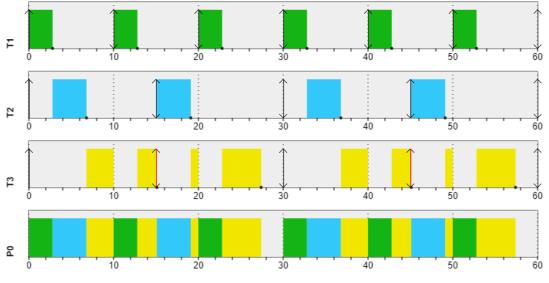

| 4.6               | Timing diagrams to determine tasks schedulability for different supply voltages                                                                 | 65       |

| 4.7               | Number of deadline misses for different voltage scale levels                                                                                    | 66       |

| 4.8               | A LITMUS trace showing response time, deadline miss, tardiness (delay)                                                                          |          |

| 4.0               | and actual worst-execution time (ACET) of different tasks                                                                                       | 66<br>68 |

| 4.9               | Throughput analysis for different voltage scale levels                                                                                          | 68       |

| 4.10 | Deadline miss of a system component on LITMUS <sup>RT</sup> even though tasks |    |

|------|-------------------------------------------------------------------------------|----|

|      | meet the utilization bound (a 74% use of the CPU)                             | 68 |

| 4.11 | Analysis of the monitored data for resistive voltage divider                  | 70 |

| 4.12 | Accuracy analysis of measured voltage                                         | 72 |

# List of Tables

| 2.1 | A taskset with different requirements in a multiprocessor system                                                        | 22              |

|-----|-------------------------------------------------------------------------------------------------------------------------|-----------------|

|     | AADL components to C++ Code mapping                                                                                     |                 |

|     | Cost estimation using COCOMO for writing OpenMP parallel programs<br>Cost estimation using COCOMO for writing AADL Code | $\frac{58}{59}$ |

# Abbreviations

| RTS                                               | Real-Time System                               |  |

|---------------------------------------------------|------------------------------------------------|--|

| $\mathbf{RTSs}$                                   | Real-Time Systems                              |  |

| AADL                                              | Architecture Analysis & Design Language        |  |

| UML                                               | Unified Modeling Language                      |  |

| OpenMP                                            | Open Multi-Processing                          |  |

| $\mathbf{QoS}$                                    | Quality of Service                             |  |

| MDA                                               | Model Driven Architecture                      |  |

| NIST                                              | National Institute of Standards and Technology |  |

| $\mathbf{R}\mathbf{M}$                            | Rate Monotonic                                 |  |

| <b>EDF</b> Earliest Deadline First                |                                                |  |

| $\mathbf{MC}$                                     | MC Mixed Criticality                           |  |

| <b>DVFS</b> Dynamic Voltage and Frequency Scaling |                                                |  |

| COCOMO                                            | Constructive Cost Model                        |  |

| LOC                                               | Line of Code                                   |  |

| TAR                                               | Test Accuracy Ratio                            |  |

| DUT                                               | Device Under Test                              |  |

| MILNP                                             | Mixed Integer Nonlinear Programming            |  |

| API                                               | Application Programming Interface              |  |

| CPS                                               | Cyber-Physical Systems                         |  |

# Chapter 1

# Introduction

Real-time embedded systems are those systems that require to respond within strict time constraints and provide a worst-case time estimate for critical situations. Typically, realtime embedded systems are classified into two types, hard and soft RTSs. The hard RTSs consider any missed deadline to be a system failure. A deadline of a task is a specified time indicating when a task to be completed. On the other hand, a soft RTS allows a task to miss the deadline, but the system service is degraded. However, we usually see most of the hard RTSs can tolerate a certain delay that is defined by the system user, not allowing to cross the delay limit. Therefore, these systems are called weakly-hard RTSs [3][4]. For example, a control system application can tolerate some delay during its execution. In this system, the distribution of its task requirements and missed deadlines during a window of time is precisely bounded. The embedded system applications differ from each other in terms of their design and requirements. The requirements are defined as timing requirements and QoS requirements. The QoS requirements are translated as timing requirements. The high QoS requiring tasks need deterministic execution where the other tasks may not always require deterministic execution. A system needs to satisfy those requirements by computing application tasks into different platforms.

To meet the increasing demand for high-performance computing, the use of multiprocessor systems is growing rapidly. The design of embedded system applications in these multiprocessors is becoming very complex due to the integration of various applications into a single platform. However, the programmers experience many implementation challenges (e.g., mapping application tasks, changing performance requirements) while writing parallel programs for multiprocessors. In order to overcome the implementation challenges [5], many programming frameworks enable execution of tasks in parallel by substantially raising the level of abstraction in implementation. Although many programming frameworks exist, the application designers face difficulties in mapping specifications to tasks with varying requirements [6].

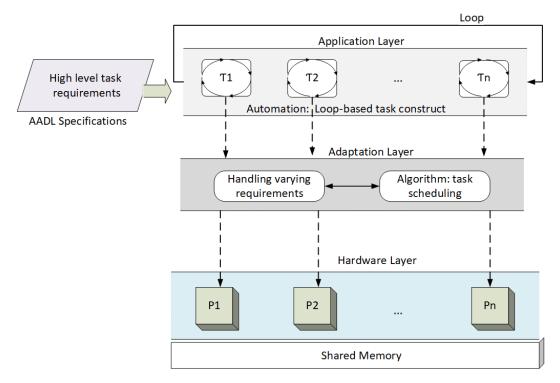

Moreover, an embedded system executes a number of tasks on different components (e.g., hardware and software) where each task is required to complete its operation within a stringent timing deadline utilizing limited computing resources. In any dynamic environment that changes frequently, a system including integrated components requires robustness in generating the correct output. The robustness requires a system or component to operate correctly in the presence of invalid input or stressful situation [7]. The output of a task requires to represent a good QoS of the system or components. Therefore, embedded systems need to be implemented carefully to automate the design process that maps high-level requirements and monitors the task's output for meeting the requirements of the parallel tasks.

## 1.1 Design automation of parallel periodic tasks

Embedded system applications execute different types of tasks [8] that are hard realtime, soft real-time, and non real-time. In this thesis, we assume tasks that are not hard real-time but may enforce timing requirements weakly to achieve a high QoS. Moreover, embedded system applications execute tasks periodically for a long time until the system is out of service. This requires application tasks to execute repeatedly with predictable execution times. Therefore, embedded systems with soft real-time tasks require a parallel programming environment to run independent tasks repeatedly in predictable times. As an example, a home automation system may have multiple applications that periodically monitor a predetermined area for an emergency state comprising various tasks like smoke detection, carbon monoxide (CO) detection, capturing images, and measuring temperature. Each of the tasks is scheduled to run repeatedly after every fixed time unit. This repeated task execution requirement can be controlled using a loop.

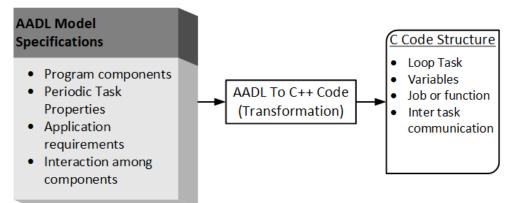

#### 1.1.1 Mapping of AADL specifications to a loop-based task construct

In any embedded system application comprising of periodic tasks, each task requires to run concurrently to assure the better safety of the monitoring area. To achieve task-level parallelism upon a multiprocessor platform, we can execute the multiple independent tasks at the same time and accelerate the performance of the system [5]. However, such requirements and the parallel programming interface syntax often impose various design constraints to automate the high-level application requirements as defined in specification languages such as Architecture Analysis and Design Language (AADL) [9]. An AADL specification defines various kinds of software and hardware component types such as systems, processes, threads, processors, and buses.

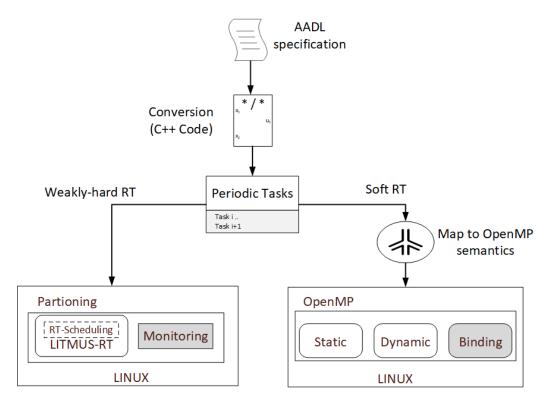

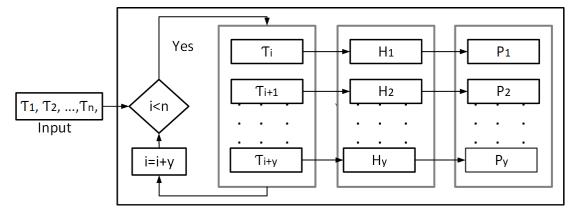

In this thesis, we propose a loop-based task construct that helps us to map the high-level requirements of periodic tasks into task constructs of a parallel programming interface. We see the increasing use of multiprocessing API called OpenMP to overcome the design and implementation challenges [10] in soft RTSs. OpenMP is a parallel programming interface that offers loop-based language constructs in addition to the thread-based execution abilities by for loop iterations. This seems a perfect fit for running soft RTS applications because of the repeated behavior of tasks. Thus, in this work we present an automatic conversion of our AADL-based task constructs into the loop-based task constructs for OpenMP in soft RTSs. Besides, we use the loop based task construct to run in weakly-hard RTSs and monitor the task output for calibration in LITMUS<sup>RT</sup>.

#### 1.1.2 Task scheduling

We analyze different scheduling approaches for parallel periodic tasks which are available in OpenMP and LITMUS<sup>RT</sup>. OpenMP offers different scheduling algorithms to run the tasks in the system. It is essential to analyze the performance of execution times for different scheduling algorithms because of the varying requirements of embedded system applications. Therefore, in this design approach, we focus on soft real-time embedded applications with requirements of the high and low QoS, leaving the extension to other types of systems in the future. We perform a detailed analysis of static and dynamic [10] approaches offered by OpenMP to analyze the differences in execution timing behavior. Moreover, we examine the static, dynamic and rate monotonic scheduling approach to provide better throughput and response time for tasks focusing on QoS [11, 12].

## **1.2 QoS Requirements preservation**

To preserve the application requirements, our designed framework includes an adaptation layer that guides to select the right scheduling policy based on the requirements of tasks in soft RTSs and a monitoring framework to ensure the expected output in weakly-hard RTSs. Therefore, we explain how the QoS requirements are adapted and what challenges exist toward the implementation of the adaptation layer.

#### **1.2.1** Requirements adaptation layer

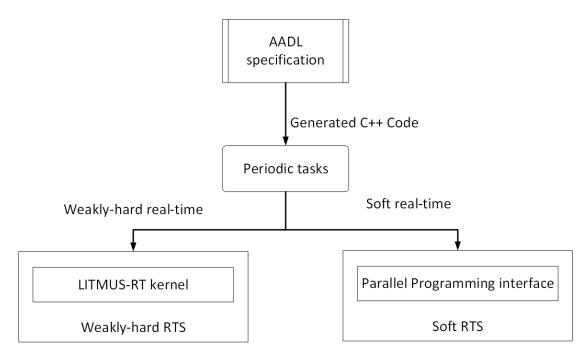

In our proposed design approach, we achieve a tighter bound on execution time on multiple runs of the same task by binding program execution threads to processors. We also provide flexibility in choosing the scheduling approaches for different requirements. The designed framework includes an adaptation layer where we can define different configurations to meet the high-level requirements of applications. In this work, we assume two types of requirements for tasks which are of high QoS and low QoS. As an example, in an obstacle detection avoidance scenario, a robot requires to get all the updated data (e.g., image) from all the sensors. Therefore, the communication for transmitting data for detecting and avoiding obstacles define the QoS of the task. For instance, whenever a robot follows a straight line, the obstacle detection sensors should transmit the data at the highest rate for detecting and avoiding obstacle where the line sensors can be scanned at a lower data rate. As a result, the obstacle detection task demands a high QoS requirement by maintaining high transmission of data within a certain time. On the contrary, the line follower data transmission at a lower rate can be leveled as a low QoS requirement as it is following a straight line. These QoS requirements are interpreted as timing or output accuracy requirements. Therefore, we consider QoS requirements for soft and weakly-hard RTSs in our thesis work. Figure 1.1 shows the abstract view of our thesis workflow for different RTSs.

#### 1.2.1.1 Satisfying QoS requirements for soft RTSs

In the case of soft RTSs, a task is expected to complete within a certain time but failing to meet the requirements does not have any catastrophic failure. Therefore, the use of the OpenMP parallel programming framework to implement such soft RTS applications can help to automate the design process and meet the QoS requirements more adequately. The high QoS requirement refers to meeting timing requirements predictably where the low QoS requirement does not require to run deterministically due to the best effort execution behavior. To meet the high QoS requirement of tasks, we propose the OpenMP static scheduling approach with the addition of using processor affinities. The thread to processor binding design makes it possible to assign tasks into processors

FIGURE 1.1: An abstract view of our design automation and requirements preservation workflow

deterministically because of controlling a task where it will execute. Such a fixed assignment of tasks to processors reduces the number of migrations among processors. Binding tasks to threads for mapping to processors during scheduling takes the advantages of data locality and therefore minimizes the synchronization overhead significantly. This results a tighter bound on execution time for tasks executed repeatedly. On the other hand, we use the dynamic scheduling approach for running low QoS requirement of tasks that require faster execution.

#### 1.2.1.2 Satisfying QoS requirements for weakly-hard RTSs

To preserve the QoS requirements in weakly-hard RTSs, we present a monitoring approach using a real-time kernel (LITMUS<sup>RT</sup> [13]) and partitioned multiprocessor Rate Monotonic (RM) scheduling algorithm. This monitoring approach monitors the accuracy of system components to ensure the expected output concerning the QoS requirement. Therefore, we propose a calibration framework that monitors the component's output accuracy and guides to take action if the output deviates from the expected result. To understand the accuracy-related QoS requirements, we discuss first the basic terminology regarding the component's accuracy in embedded systems.

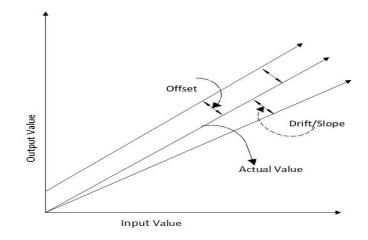

A component of a system deteriorates over time, and therefore the performance degrades gradually. Different uncertainty factors such as aging of the software of a component, environmental changes, normal wear and tear of the hardware involving in a component, and process changes can cause deterioration on the accuracy. Therefore, a deteriorated system component produces a deviated output that includes various offsets, drifts, and noises. This results in the component's output accuracy that determines the correctness of output compared to a standard value. In embedded systems, the fulfillment of realtime requirements depends on a certain level of accuracy. For example, the electronic speed control in any aircraft needs to produce a correct speed before its landing, otherwise an incorrect output while measuring speed can lead to an undesirable consequence.

In order to ensure an expected accuracy, automatic periodic calibrations are performed to estimate error in output against the known calibration standards (e.g., NIST) [14] and corrections are made to minimize errors. In measurement science, calibration is a way of comparing the measurement values delivered by a component or device under test with a standard calibration device that has a known accuracy. In practice, calibration also includes output error adjustment of the component if it is out of the accepted range of accuracies. The standard calibration components are assumed to provide correct measurements. Most of the system components are calibrated against the highest level of standards such as international, national, primary, secondary and laboratory standards. However, in the case where such externally defined standards are absent, a user-defined standard can also be developed by different methods such as log correct output or trace data patterns taken from a high accuracy system component. To ensure a fair measurement of accuracy in the calibration process, different measurement communities recommend maintaining a test accuracy ratio (TAR) 4:1 [15], which is the ratio of accuracies between a standard and a unit under test. The ratio of TAR means the standard components should be four times more accurate than the unit under test.

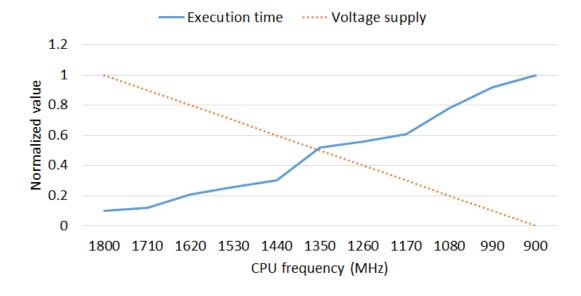

The QoS degradation of a component due to inaccuracies may cause a task to miss the requirements (e.g., deadlines). For example, energy-aware scheduling algorithms use dynamic voltage and frequency scaling techniques where the output voltage supply provided by a voltage divider is required to maintain a certain accuracy to guarantee a task deadline. However, an incorrect measurement in producing the voltage supply causes an undesired clock frequency. Figure 1.2 shows how a task execution time changes while we modify the supply voltage for different CPU clock frequencies. This eventually provides an execution time delay for which a task may miss the deadline and a deadline miss may lead to a component or system failure eventually. To avoid such occurrence, it is required to perform calibration, but we need to analyze when a component needs it.

FIGURE 1.2: Execution time changes for different CPU frequencies [1]

#### 1.2.2 Monitoring task output for calibration

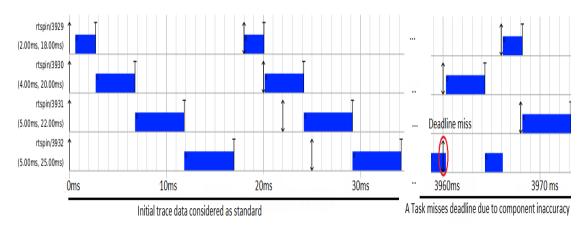

In this thesis, we propose a calibration framework for weakly-hard real-time systems to determine whether we need to take any recovery actions of a system component immediately or we can wait by leveraging the low utilization of a system to delay the recovery process which is usually expensive. The laxity on the timing requirements of tasks is considered without compromising any safety requirement (i.e., deadline misses). Unlike the existing studies, we present a calibration framework that aims to increase the robustness of a system by monitoring the correctness of measured values and reviewing task schedulability. Moreover, we allow provisioning of the increase in the execution time and the deadline of a task based on the available CPU utilization and a user-defined tolerable delay. On the other hand, a schedulability test is proposed with the consideration of the accuracy of a system component using the rate monotonic task scheduling. Moreover, the component's output accuracy affects the QoS of a task. Thus, our proposed framework records all the related system input, output, and scheduling traces upon a task execution to monitor the component accuracy and measure the quality of a task output. To perform calibration, our experiment in LITMUS<sup>RT</sup> defines the initial

trace data of a component as a calibration standard and shows the necessary steps that are required to correct the output.

## **1.3** Challenges in requirements preservation

The design and implementation of embedded system applications with varying requirements are challenging. The implementation requires the proper design in which area the requirements should be handled. On the other hand, the designers face challenges in mapping requirements to any implementation approach. Such kind of interactions often makes it more complex to automate the development process of embedded software.

#### **1.3.1** System-level formal specification

The high-level specification of embedded system application is mainly based on informal requirements. Most of the cases, it does not fulfill the actual requirements. Moreover, it is challenging to design any application for multiprocessor systems. Assigning tasks at runtime and addressing requirements according to specification introduces difficulties for both programmers and designers. As a result, the designer and programmer have confusion regarding the mapping of requirements at design and implementation levels. However, it is also difficult to specify the whole specification at the very beginning due to the limitations of the programming language barrier, time, security, cost and performance issues [16]. Therefore, it requires design automation to ease the development process in embedded systems.

#### 1.3.2 Embedded software complexity

Nowadays, the number of lines of source code for developing embedded system applications is growing with multiple requirements of customers. As a result, embedded software takes the maximum budgets of implementation. Moreover, the design complexity of the software component causes serious concerns for the final application [16]. In general, the design of an embedded system requires verification of the system and the long redesign cycles make it more complex in the development process.

#### **1.3.3** Requirements integration

In embedded system design, we observe several domain-specific modeling languages (e.g., UML, AADL) that are practiced for different purposes considering performance, expertise, cost, safety, and security, etc. For example, UML (Unified Modeling Language) is known as a general modeling language and SysML (Systems Modeling Language) is used in systems planning related applications. However, AADL is used for many embedded software architecture designs to handle different high-level requirements. Moreover, it illustrates the system constructs such as threads, processes or processors to model real-time, safety-critical embedded systems. Moreover, it provides an advantage to model embedded system applications by analyzing task schedulability, and safety characteristics. The automatic code generation from AADL specifications drastically optimizes the executable code writing. System design is the process of deriving, from requirements, a model from which a system can be generated more or less automatically.

#### **1.3.4** Selection of a task scheduling approach

We study different scheduling approaches that have their own benefits in different scenarios. The OpenMP parallel programming framework offers dynamic and static scheduling approaches. The current static approach in OpenMP runs reasonably in guaranteeing predictable execution times for deterministic applications but it shows non-repeatability behavior in producing a similar result on multiple runs and fails to meet a predictable execution [17]. Thus, finding a way to ensure the deterministic execution of parallel programs is also an important research question for us in this work. Similarly, the weakly-hard real-time systems require the real-time kernel to ensure the timing guarantee. As an example, the LITMUS<sup>RT</sup> kernel provides different scheduling approaches like Earliest Deadline First (EDF) and Rate Monotonic (RM) where partitioned multiprocessor RM scheduling approach provides more reliable condition to meet the deadline of higher priority tasks over EDF approach.

### 1.4 Thesis objectives

To automate the design of embedded software, we find a variety of abstraction levels, execution platform, implementation approaches, and application requirements that are not supported by only one development tool. As a consequence, neither a design approach nor a single parallel programming framework supports the diversity of embedded software implementation. The multiparadigm modeling approaches are performed to integrate the design model and automate the code generation for implementation. Therefore, the main objective of this thesis is to automate the design process for mapping high-level requirements to lower-level implementation. During the automation process, we meet the requirements of the application at different levels by increasing substantial abstraction in soft and weakly-hard RTSs.

## 1.5 Contributions

In summary, the main contributions of this thesis are two-folds:

- 1. **Parallel Loop-based Task Construct:** We automate the multiprocessor embedded system application design using a parallel loop-based task construct from AADL models that map the tasks high-level requirements and their properties to the semantics of a parallel programming interface.

- 2. **Requirements Preservation:** To satisfy various tasks requirements, we include an adaptation layer that helps to satisfy tasks requirements without making any changes at the operating system level. In this work,

- we propose to bind the program execution threads to processors in OpenMP static scheduling to achieve a tighter bound on the deterministic execution time for high QoS requirement of tasks but use OpenMP dynamic scheduling for low QoS requirement of tasks. These requirements are adapted through the OpenMP parallel programming framework in soft RTSs.

- we also present a calibration framework that monitors the output accuracy of components in weakly-hard RTSs. It includes an accuracy-based task schedulability test that guides to calibrate a system component when required.

## **1.6** Organization of the thesis

We organize the thesis in five chapters. In Chapter 2, we discuss the design automation and requirements preserving related works and basic terminologies that will help to follow the remainder of our thesis work. This chapter contains the recent design automation techniques; task scheduling approaches in multiprocessor and different monitoring approaches including calibration for ensuring the correct output of embedded systems. In Chapter 3, we demonstrate the workflow of our proposed design automation framework and discuss the proposed approaches to preserve requirements. The proposed approach considers the QoS requirements preservation in soft and weakly-hard RTSs. The calibration framework monitors the system output to ensure the expected accuracy. Moreover, we show an illustrative example of how a software-based calibration can be performed when the calibration standards are not available. In Chapter 4, we present the experimental analysis of the thesis that has different sections for understanding the advantages of our proposed approaches. The experimental results include the analysis of requirement preservation approach using OpenMP in soft RTSs and output monitoring for calibration in weakly-hard RTSs. Finally, Chapter 5 concludes the thesis and points out possible future research directions in the context of requirements preserving design automation of embedded software.

# Chapter 2

# Literature review

## 2.1 Introduction

The architecture of multiprocessor is becoming more attractive for embedded systems. Embedded systems can be classified into three types which are hard, weakly-hard and soft. The hard real-RTSs are not allowed to miss the deadline of tasks. On the other hand, weakly-hard and soft RTSs have some flexibility in terms of deadline miss. However, the current hard RTSs are designed in such a way so that it can tolerate a certain level of permissible delay. These are often called weakly-hard RTSs.

Moreover, the current soft and weakly-hard RTS applications comprise of varying requirements that are increasing every day. To satisfy varying requirements, the design of embedded systems becomes more complicated as the number of components, implementation classes, modules, and methods are integrated into a particular system [18]. Although there exist a lot of works to design systems on a uniprocessor, the number of attempts for multiprocessor embedded systems are not much explored. We examine a few parallel programming frameworks for writing parallel programs but the requirements mapping in these frameworks requires a lot of efforts. Existing parallel programming interfaces are also not suitable for hard or weakly-hard RTSs. To address this issue, the structure of the abstraction level for mapping requirements of tasks is continuously advancing. A few works show the different techniques to automatic code generation but the requirements are not preserved properly. Therefore, the development process for embedded systems design from high-level requirements requires a framework to preserve requirements in design automation.

# 2.2 State of the art of design automation and requirements monitoring

An embedded system is a computing system that is designed to execute different functions. In recent time, the properties of hardware, software, and environments are changing rapidly. As a result, the embedded system design requires different techniques for predictable execution and adaptation of system requirements. The current practices for embedded system designs are:

#### 2.2.1 Language-based design

In this approach, the embedded software design follows either traditional software implementation methods or synthesis-based methods that evolve from hardware design methodologies. A classic language-based design supports a specific programming language for a targeted system. As an example, Ada and RT-Java languages.

#### 2.2.2 Model-based design

In recent trends, the hardware and software specifications are combined to design the embedded systems. This approach has substantial control over the other design approaches as it emphasizes the separation of two different levels (e.g., design level and implementation level). Due to the independence of two levels, the semantics of abstract system also increases. The model-based approaches mainly focus on producing an efficient code generation as it requires to implement sperate code for hardware and software components. A simplified model-based approach is the use of MATLAB Simulink which includes the simulation engine to define different operational properties [19][20].

However, the recent modeling languages are UML and AADL that emphasis on system architecture as a means to organize computation, communication, and constraints. UML is commonly used for the implementation of embedded system applications and provides an opportunity to generate source code for both hardware and software.

Similarly, the AADL specification assists in the design process by identifying design errors before any application implementation. Moreover, it helps to generate highquality AADL code that can lower the development costs. The advantages of using AADL in automation are listed below.

• AADL provides a standard format with correct syntax and semantics.

- It presents the software architectures overview which can be modified to integrate different properties of applications. For example, task schedulability, safety, communication latency, hardware components, software components and so on.

- It enables advanced tracking of modeling and analysis. The specification includes the system structure and runtime behavior.

- It supports code reusability in implementation approach.

However, we find a few tools to convert the AADL specification to expected program code but Ocarina [21] is one of them. It analyzes the AADL specification and produces the code for application implementation. Since it has a modular architecture, it can support customized functionalities to use its existing codes. The main features of Ocarina are:

- Parser: Ocarina supports both AADL1.0 and AADLv2 and able to parse syntaxes to a particular language.

- Code generation: The conversion of code is mainly targeted for C real-time OS.

- Model checking: Ocarina can map AADL models onto Petri Nets.

- Schedulability analysis: It also provides a mapping of AADL models onto Cheddar that analyzes the real-time performances.

#### 2.2.3 Implementation approaches in a multiprocessor platform

With increasing demands of high-performance computing and different requirements, the use of multiprocessors embedded systems is increasing. In recent works, we see the programmers use different parallel programming framework to run the applications in parallel. However, the designers face challenges in mapping high-level requirements to a parallel programming interface. Existing approaches like model-based automotive partitioning and mapping [22] use the AMALTHEA tool platform in developing automotive embedded multiprocessor systems. Through the interfaces of AMALTHEA, a user can develop different AUTOSAR (Automotive Open Systems Architecture) applications. Although the model-based design addresses various challenges considering the parallel exploitation, it can be further extended to automate the high-level requirements mapping to the lower levels. In another research, High-Level Cost Model [23] is used to automatic task level parallelization for multicore embedded systems. In this work, they use Augmented Hierarchical Task Graphs including several optimization techniques in order to perform an automatic partitioning and mapping of software to heterogeneous hardware. Ceng et al. [24][25] present MAPS (MPSoC Application Programming Studio) which performs a semi-automatic task-level parallelization.

With regard to parallel programming interfaces, several kinds of computer program parallelization standards are available in the literature like OpenMP, MPI, and CUDA. The MPI usually works better in a distributed system with a cluster environment, where CUDA is more used for GPU computation. In the recent works, the ScalScheduling [26] shows an improvement of the traditional interactive application design which overcomes the data transfer rate as well as the task scheduling latency over the network. However, the OpenMP task parallelism technique is well-known for shared memory architecture in a multiprocessor system. In the OpenMP task parallelization technique, each task is created inside a parallel region with a thread that can split itself into a number of threads following the fork and join model.

OpenMP 4.5 and 5.0 introduces a tasking model that supports both task dependency and nested task parallelization. Recent work shows an extension to OpenMP 5.0 that improves the taskwait barrier and task dependencies from an inner task to outer task exposing more parallelism [27], but still, there are no significant changes in the improvement of task scheduling approaches. The OpenMP 3.0 [28] version has different loop scheduling techniques which can be implemented using #pragma omp parallel for schedule () [10]. The choice of scheduling types (e.g., static, dynamic) depends on the application type and their requirements. A proper selection of scheduling technique can result in substantial performance gains [29]. Considering this goal, an adaptive scheduler [30] is designed for an OpenMP compiler that helps to find the best scheduling policy reducing the number of threads at runtime.

In a recent study, Melani et al. propose a static scheduling approach that enables safetycritical OpenMP applications [11]. In their proposed method, they focus on deriving the optimal mapping of task-parts to threads using ILP formulation by introducing a static allocation model for tied and untied tasks. In addition, TG-PEDF [31] shows a new way of scheduling mixed-criticality tasks based on high- and low-criticality tasks grouping. It implements MILNP formulation to analyze the tasks grouping, and the evaluation of this strategy outperforms the mixed-criticality (MC) scheduling algorithm. In another study, a new benchmark suite OpenTGB presents a way to collect real-time tasks and transform them into task graph model [32]. The OpenTGB makes the real-time tasks eligible for scheduling efficiently by defining a new response time bound.

In our work, we demonstrate a general framework for applications with varying requirements and modify the OpenMP static scheduling approach for deterministic task execution. This framework will help to understand the effect of the modified scheduling for different requirements of tasks over the existing approaches in embedded systems.

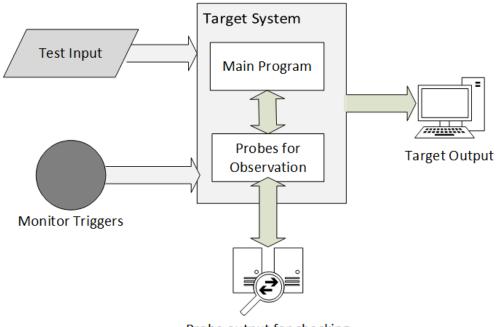

## 2.3 Approaches to monitoring

A monitoring approach involves observing the execution behavior and performance of an application to understand the insight of a software operation [33]. To monitor an embedded system, a component of hardware or software is separately integrated into the system. The attachment of the component is called a probe. A probe extracts all the information about internal operations. As shown in Figure 2.1, the probe provides the generated output from the system to compare with the expected output. This can be achieved using a hardware probe that monitors internal system signals or any software probe that performs some functionalities in order to calculate the expected output.

Probe output for checking

FIGURE 2.1: Output monitoring in embedded systems

A monitoring approach can provide a runtime verification that checks the system execution behavior and provides notification if any unexpected situation occurs at runtime. The execution behavior of the system is specified against the application's software requirements. Assuring the correct behavior and output of embedded systems is always a challenging job. In a traditional approach, a runtime verification can provide a solution in finding errors and the reasons behind those errors. A monitoring approach may vary in terms of the spheres of embedded systems.

#### 2.3.1 Hardware Monitors

In modern embedded systems, the designers examine different kinds of metrics like cost, power, performance, resource utilization and so on. These parameters can be visualized and monitored through a hardware probe. The monitoring of these parameters can verify the actual output of the system.

One advantage of using hardware monitoring is that it reduces the possibility of intrusion caused by the internal or external execution of the monitoring code. However, it has a lot of limitations like the communication to different components may interrupt the actual execution and performance of tasks.

#### 2.3.2 Software monitors

In the case of software-based monitoring, a software program is integrated into the operating system, or it can be executed via external hardware. The program code needs to be executed along with the main program which might cause a delay in the execution of the software code. The main advantage of a monitoring approach is that it can have access to a large amount of information of a complex embedded system [34].

#### 2.3.3 Hybrid monitors

Another popular monitoring approach is hybrid monitoring that combines both the hardware and monitoring approaches. As a result, it can provide more support than others. At the same time, it alleviates the disadvantages of other approaches as it uses physical interfaces that have less interference with the system and captures the maximum information through software components. The hybrid approach may experience an overhead for executing additional software code which likely affects the behavior and performance of embedded systems, but the consequences can be diminished associating the hardware monitoring.

### 2.4 Task scheduling approaches in multiprocessor systems

With the increasing availability of multiprocessors, many RTSs prefer the multiprocessor architecture for high computational tasks. Although the multiprocessor systems support parallel tasks execution, still, research is ongoing to find better strategies to schedule tasks efficiently. To schedule, a n number of tasks on a m number of processors, few scheduling algorithms show some advantages and disadvantages related to the deadline miss and overall performance. Moreover, the characteristics of multiprocessors are also important in tasks scheduling. Multiprocessors can be categorized as follows [2]:

- Type 1: each processor possesses similar computational rate and abilities,

- Type 2: each processor has a similar configuration of capabilities including varying speeds, and

- Type 3: each processor is separated from each other and heterogeneous.

One of the significant contributors to the multiprocessor scheduling problem is resource allocation. This problem states that the scheduling algorithm requires to map the appropriate task in the proper processor. Besides, it demands the timing guarantee for each task to ensure the stability of the system.

### 2.4.1 Scheduling approaches

In embedded multiprocessor systems, the static, dynamic, partitioned, and global [2] scheduling algorithms are frequently used to schedule the tasks. In addition, we see increasing use of rate monotonic scheduling approach for meeting the deadline of high priority tasks in embedded systems.

**Static scheduling:** In the static scheduling approach, the execution of tasks is controlled following a specific order that defines how the program execution threads will be running in the code at compile time. In any application, if it requires to control (e.g., lock, semaphores, joins, and sleeps) the threads to fulfill the requirements, the static scheduling approach is practiced generally. The partitioned scheduling approach eventually follows the static approach which is discussed in the later part. **Dynamic scheduling:** The dynamic scheduling approach does reflect any control over threads. In this case, the thread scheduling is done by the operating systems based on any scheduling algorithm implemented in OS level. The order of threads execution depends on the integrated algorithm except the control is defined at compile time. However, this approach also establishes an order of execution, but the hardware performs this rather than the compiler. The dynamic scheduling shows faster task execution than the static scheduling as it has a free flyer without any intentional waits.

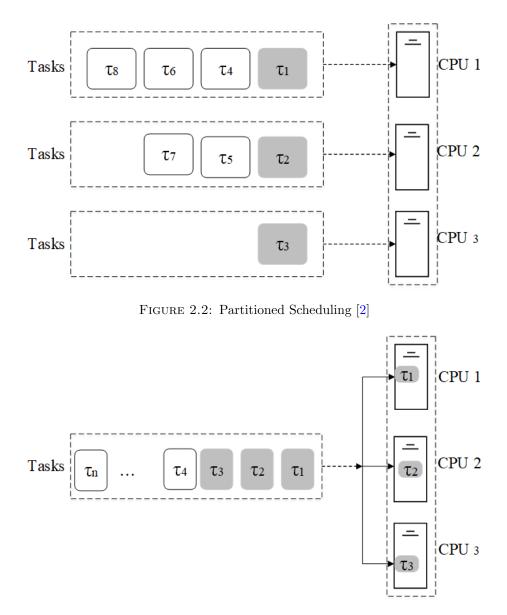

**Partitioned scheduling:** A partitioned scheduling algorithm allocates resources for an individual task to a particular processor [2]. Fig. 2.2 shows an example of partitioned scheduling each task  $\tau_i$  is assigned on the individual processor. For example,  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are running separately in processor *one*, *two* and *three* respectively where processor *three* will remain idle later as no task is assigned in it. The partitioned scheduling algorithm has both pros and cons. The algorithm has the following advantages:

- It allows static task assignments.

- Partitioned scheduling supports most of the single processor scheduling approaches.

- If any high-criticality task runs on overrun mode, it affects only the task-associated processor where other processors remain unaffected.

- As tasks are not allowed to switch the processors, there is no migration cost.

- To design partitioned scheduling algorithms, each processor maintains a separate queue for handling tasks.

The principal limitations of partitioned scheduling algorithms are listed below:

- This algorithm cannot help to share all the available resources equally

- Since tasks avoid migration, the system may experience a low processor utilization

- Although any processor can become idle at runtime, it cannot be assigned for mapped tasks to other processors.

**Global scheduling:** Using a global scheduling algorithm, all the tasks can also be scheduled upon multiprocessors. The global queue cannot be applied to overcome the multiprocessor scheduling problem in safety-critical systems because it allows task migration among the available processors. The migration of any task usually adds extra

FIGURE 2.3: Global Scheduling [2]

overhead, and the system may show unpredictable behavior due to the dynamic changes in the task environment. Since the algorithm maintains a single global queue, the implementation and design become more complicated for different mixed-criticality applications [2]. Fig. 2.3 presents an example of global scheduling where  $\tau_4$  may be scheduled but it can never happen in partitioned scheduling approach. In comparison with the partitioned scheduling approach, the advantages of global scheduling are given below:

- All the immediate tasks are kept in a single global queue.

- Since task migration is allowed, the global scheduling ensures the maximum resource utilization.

• Most of the multiprocessor operating system now supports global scheduling.

On the other hand, some of the limitations of this approach are addressed below:

- Most of the uniprocessor scheduling algorithms cannot utilize the processors completely in multiprocessors.

- Task migration may lead to an unpredictable state for the safety-critical system.

- Due to task migration, various processors may cause varying computational rates which decrease the optimal performance.

- Tasks migration causes an extra overhead in the system because all the processors use shared memory for communicating among them.

- This approach may provide poor resource utilization for high-criticality tasks because of the prioritization of low-criticality tasks.

**Rate monotonic:** The Rate Monotonic scheduling approach assigns priorities to different tasks according to their time period. If the time period of a task is small, it will have the highest priority in case of execution. This approach follows the task preemption policy where a higher priority task can preempt the lower priority task from its execution. A given task is schedulable in an RM scheduling approach if it passes the schedulability test which is given in equation 2.1.

$$U(\tau) = \sum_{1}^{n} \frac{e_i}{T_i} \le n(2^{\frac{1}{n}} - 1)$$

(2.1)

Here,  $U(\tau)$  represents the resource utilization,  $e_i$  is the computation time,  $T_i$  is the release period and n is the number of tasks.

#### 2.4.2 Schedulability test

To schedule successfully any periodic task set on m processors can have utilization  $U(\tau)$  no greater than  $\frac{m^2}{2m-1}$  [35].

$$U(\tau) \le \frac{m^2}{2m-1} \tag{2.2}$$

In a safety-critical system, the partitioned algorithm is used more than the global scheduling upon a multiprocessor platform. The reason behind the choice of partitioned scheduling is to use the processors better where global scheduling shows more unpredictability due to processor migration and unavailable cache information.

| $\tau$   | Requirement | Deadline | ExecutionTime |

|----------|-------------|----------|---------------|

| $\tau_1$ | Low QoS     | 2        | 1             |

| $	au_2$  | High QoS    | 5        | 2.5           |

| $	au_2$  | High QoS    | 5        | 3             |

TABLE 2.1: A taskset with different requirements in a multiprocessor system

For example, Table 2.1 shows a set of tasks and these tasks have different requirements that need to be achieved. When scheduling these tasks in a 2-core system, the schedulability test using Equation 2.2 indicates that the tasks are not schedulable in static scheduling because process utilization is higher than the defined value. Therefore, not all tasks meet their deadlines.

CPU utilization calculation:

$$\Rightarrow \text{LCM}(2, 5, 5) = 10$$

$$\Rightarrow \text{U}(\tau) = \frac{1}{2} + \frac{2.5}{5} + \frac{3}{5} = 1.6$$

$$\Rightarrow \text{U}(\tau) \nleq (\frac{\text{m}^2}{2\text{m}-1} = \frac{4}{3} = 1.3)$$

In uniprocessor and multiprocessor systems, once system utilization becomes higher than the optimal value, then the low-criticality or high-criticality tasks are not guaranteed to be scheduled to meet the deadlines.

Nevertheless, existing schedulability tests are not always enough to guarantee the timing behavior of a task if the other important factors like component's accuracy and reciprocal interference produced by the concurrent access to the shared memory resources are not examined correctly. Such factors can introduce lower data processing rate, variable delays, and jitter in the execution of tasks for which a system may lead to an unstable state with performance degradation [36]. Therefore, Yifan et al. [37] propose a general methodology to select the proper parameters for real-time controllers in resource-constrained systems. In this work, it shows that the selection of an appropriate period and deadline [38] can substantially improve the control performance in embedded systems. The experimental result in TrueTime [39] indicates the performance improvement where the tasks are scheduled using EDF on a uniprocessor system.

## 2.4.3 Accuracy-related task scheduling

A number of task scheduling algorithms are available in embedded systems where the selection of an algorithm depends on the requirements of the systems. Most of the popular existing algorithms are familiar with the timing guarantee and efficient resource utilization of tasks. However, the correctness of output and QoS of a task are not discovered much compared to other task parameters. Existing embedded control systems have a tendency to tolerate a certain amount of inaccuracy in the task output. Following a similar concept, Buttazo et al. [40] propose an elastic task model where a task can intentionally change their execution rate for the different quality of services. Considering the current workload of a system, many QoS guided algorithms [41] are proposed that focuses on achieving high throughput and minimum execution time to keep the system stable.

To achieve the expected output, many research works focus on the selection of different parameters of a task which investigate the system performance and guarantee stability [42]. After that, different real-time task scheduling algorithms such as RM or EDF are applied for task schedulability analysis to ensure whether a task is able to complete its execution within the assigned deadline or not [43]. However, a system may experience an overload situation when it runs with limited resources than the required. As a result, many tasks may take a longer time to be executed than the usual time that is considered at the beginning of the design process. Thus, it shows the necessity to have a task schedulability test considering the worst-case execution time of all the tasks.

Mitra Nasri et al. [44] propose a scheduling algorithm depending on accuracy-constrained RTSs where two sources of data inaccuracy are considered like data noise and age of data. The defined accuracy of the work is regarded as a function of data noise which eventually indicates the QoS of a task output. In another work, Lin Huang et al. [45] propose a technique to improve the non-preemptive real-time scheduling allowing imprecision in the computation. As a result, a task that does not affect much for its timing violation can be computed differently to achieve schedulability.

On another work, Bini and Cervin [46] show a way to calculate an approximate delay as a function of task periods and other obstructions that come during the performance optimization. As delays have an impact on the control performance, the proposed approach estimates an additional delay at design time so that it can significantly reduce the implementation-related performance degradation. It demonstrates that the proposed co-design method with fixed priority tasks provides a lower cost than previously offered period assignment schemes. However, in our work, we illustrate the DVFS technique for power-aware application where the system component's output accuracy need to be considered during task scheduling. Thus, we propose a calibration framework to monitor the accuracy of a system component.

## 2.5 Calibration for real-time embedded systems