# Controlling the Vienna Rectifier Using a Simplified Space Vector Pulse Width Modulation Technique

by

Ali Sunbul

A thesis submitted to the School of Graduate and Postdoctoral Studies in partial fulfillment of the requirements for the degree of

Master of Applied Science in Electrical and Computer Engineering

Faculty of Engineering and Applied Science

Ontario Tech University

Oshawa, Ontario, Canada

November 2019

© Ali Sunbul, 2019

## THESIS EXAMINATION INFORMATION

### Submitted by: Ali Sunbul

### Master of Applied Science in Electrical and Computer Engineering

Thesis title: Controlling the Vienna Rectifier Using a Simplified Space Vector Pulse Width Modulation Technique

An oral defense of this thesis took place on November 12, 2019 in front of the following examining committee:

#### **Examining Committee:**

| Chair of Examining Committee | YING WANG                                                                                                                                                                                |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Research Supervisor          | VIJAY SOOD                                                                                                                                                                               |

| Examining Committee Member   | SHELDON WILLIAMSON                                                                                                                                                                       |

| Thesis Examiner              | DIPAL PATEL, BEng, MSc, PhD (Newcastle UK).<br>Assistant Professor. Department of Automotive,<br>Mechanical and Manufacturing Engineering. Faculty of<br>Engineering and Applied Science |

The above committee determined that the thesis is acceptable in form and content and that a satisfactory knowledge of the field covered by the thesis was demonstrated by the candidate during an oral examination. A signed copy of the Certificate of Approval is available from the School of Graduate and Postdoctoral Studies.

#### ABSTRACT

In this thesis, a simplified Space-Vector Pulse-Width-Modulation (SVPWM) technique for the Vienna rectifier is introduced to reduce the computational burden, the switching losses and the Total-Harmonic-Distortion (THD). Furthermore, the robustness of this modulation technique is tested under various faults through a 70 kW MATLAB/Simulink model and the results are validated through 1.2 kW prototype. The results reveal that the simplified SVPWM provides a low THD, unity Power-Factor (PF) and effective capacitor voltage balancing even after extreme faults.

This study introduces a multilevel Power-Factor-Correction (PFC) converter in a 2stage configuration. The first stage is the Vienna rectifier which has a high boosting ratio. To overcome this issue, a high efficiency 4-switch converter is cascaded with the Vienna rectifier. This converter employs storage-less passive components and provides a Zero-Current-Switching (ZCS) for all of its switches. A description of the converter is first introduced followed by the simulation results.

**Keywords:** PFC; Multi-level rectifier; Vienna rectifier; soft switching; space vector modulation

### **AUTHOR'S DECLARATION**

I hereby declare that this thesis consists of original work of which I have authored. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize the Ontario Tech University to lend this thesis to other institutions or individuals for the purpose of scholarly research. I further authorize Ontario Tech University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. I understand that my thesis will be made electronically available to the public.

ALI SUNBUL

#### ACKNOWLEDGMENTS

All praise is due to Allah, Lord of the worlds, the entirely merciful, the especially merciful, for His guidance during this research and throughout my life.

From the bottom of my heart, I thank my supervisor Dr. Vijay Sood for his continuous and unlimited support during this research. I also thank Dr. Vijay Sood's research group for their help throughout this research; special thanks to Ahmad Shier for his support and advices.

I also express my deep thanks and appreciation to my parents and wife for their support and prayers.

I acknowledge Taibah University and NSERC for sponsoring my education and supporting my research.

I would like to express my regards to Professor Sheldon Williamson for permitting practical validation of the converter model in his laboratory.

#### STATEMENT OF CONTRIBUTIONS

The main contribution in this thesis is implementing the simplified Space Vector Pulse Width Modulation (SVPWM) for the Vienna rectifier and verifying the robustness of this method under extreme faults. In addition, the functionality of the SVPWM method is verified by experimental results. This contribution is explained in Chapters 5, 6 and 8 and has been published in:

A. Sunbul and V. K. Sood, "Simplified SVPWM Method for the Vienna Rectifier," 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Toronto, ON, Canada, 2019, pp. 1-8.

Furthermore, a submission is in the process to:

A. Sunbul, A. Sheir, V. K. Sood, "Study of The Robustness of Vienna Rectifier Under Fault Conditions Using Simplified Space Vector", in Canadian Journal of Electrical and Computer Engineering, spring 2020, (In progress).

The other contribution in this thesis is to overcome the issue of Vienna rectifier's high boosting ratio by cascading a highly efficient second stage to it. The second stage employs a soft-switching technique and storage less passive components which keeps the system highly efficient and small in size. This contribution is described in Chapter 7 and has been published in:

A. Sunbul, A. Sheir, V. K. Sood," High Performance Multilevel Power Factor Correction Boost-Buck Converter," 2019 IEEE Electrical Power & Energy Conference (EPEC), Montreal, QC, 2019, pp. 1-6.

Furthermore, a submission is in the process to:

A. Sunbul, A. Sheir, V. K. Sood, "High Performance Multilevel Power Factor Correction Boost-Buck Converter," in Canadian Journal of Electrical and Computer Engineering, spring 2020 (Submitted).

| ABSTRACTiii                                            |

|--------------------------------------------------------|

| AUTHOR'S DECLARATION iv                                |

| ACKNOWLEDGMENTS v                                      |

| STATEMENT OF CONTRIBUTIONS vi                          |

| TABLE OF CONTENTS vii                                  |

| LIST OF TABLES xi                                      |

| LIST OF FIGURES xiii                                   |

| LIST OF ABBREVIATIONS AND SYMBOLS xix                  |

| Chapter 1. Introduction1                               |

| 1.1. Motivation 1                                      |

| 1.2. Objectives                                        |

| 1.3. Thesis overview                                   |

| Chapter 2. Background and Literature Review            |

| 2.1. Background                                        |

| 2.1.1. Problem statement                               |

| 2.1.2. Classification of Rectifiers:                   |

| 2.2. Literature Review                                 |

| 2.2.1. Direct 3-phase PFC Rectifiers:                  |

| 2.2.2. 3-phase Boost PFC Rectifiers:                   |

| 2.2.3. Modulation Techniques for the Vienna Rectifier: |

| Chapter 3. The Vienna Rectifier                        |

# TABLE OF CONTENTS

| 3.1. Introduction to Vienna Rectifier                                      |           |

|----------------------------------------------------------------------------|-----------|

| 3.2. Vienna Rectifier Topology:                                            |           |

| 3.3. The Properties of the Vienna Rectifier:                               |           |

| 3.3.1. The Degree of Freedom in the Vienna Rectifier                       |           |

| 3.3.2. The Operation of the Vienna Rectifier                               |           |

| Chapter 4. SVPWM for 2-level Converters                                    |           |

| 4.1. Introduction to Space Vector                                          |           |

| 4.1.1. Definition:                                                         |           |

| 4.1.2. Clarke Transformation                                               |           |

| 4.1.3. Park's Transformation:                                              |           |

| 4.2. Space Vector for 2-level-Converters:                                  |           |

| 4.2.1. Switching States:                                                   |           |

| 4.2.2. Space Vectors:                                                      |           |

| 4.2.3. Dwell Time Calculation:                                             |           |

| Chapter 5. Modulation and Control of The Vienna Rectifier Using Simplified | d 3-level |

| SVPWM                                                                      |           |

| 5.1. Space Vector Analysis for Vienna rectifier:                           |           |

| 5.1.2. Space Vectors for the Vienna Rectifier:                             |           |

| 5.2. Space Vector Modulation for Vienna Rectifier:                         |           |

| 5.2.1. Sector Identification                                               |           |

| 5.2.2. Angle Normalization                                                 |           |

| 5.2.3. Sub-vector Calculations:                                            |           |

| 5.2.4. Shortening Sub-vectors:                                             |           |

| 5.2.5. Pulse Generation                                                    | 59        |

| 5.3. Capacitor Voltage Balancing                                           | 61        |

| 5.4. Space  | e Vector Controller Circuit                               |                |

|-------------|-----------------------------------------------------------|----------------|

| 5.5. Imple  | menting the Simplified SVPWM                              |                |

| Chapter 6.  | Simulation Results for the Vienna Rectifier Using the Sim | plified SVPWM. |

|             | •••••                                                     |                |

| 6.1. Simul  | lation Tests:                                             |                |

| 6.1.1. T    | he Ideal Case (no fault applied)                          | 66             |

| 6.1.2. C    | apacitors Voltage Balance under Fault Condition           | 69             |

| 6.1.3. C    | apacitors Mismatch Test                                   | 72             |

| 6.1.4. C    | apacitor's Short-circuit Test                             | 74             |

| 6.1.5. L    | oad Step Change Test                                      |                |

| 6.2. Vienr  | na Rectifier's Boosting Ratio:                            | 77             |

| Chapter 7.  | The Vienna rectifier for low voltage applications         | 80             |

| 7.1. 4-swi  | tch Buck Converter                                        |                |

| 7.2. Simul  | lation Results                                            | 85             |

| Chapter 8.  | Experimental Validation                                   |                |

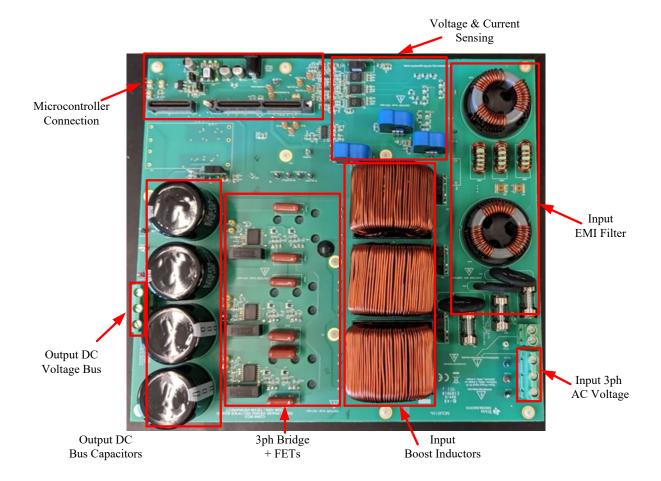

| 8.1. Break  | down of the Prototype:                                    |                |

| 8.1.1. V    | ienna Rectifier Power Stage:                              |                |

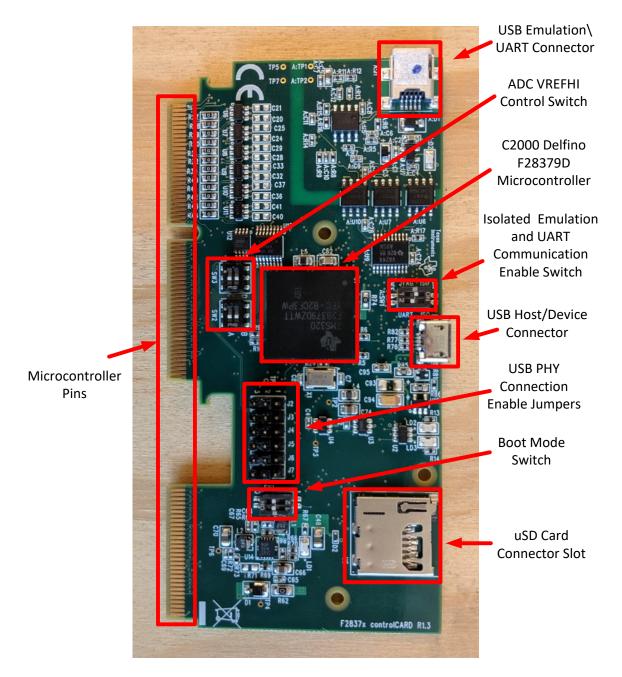

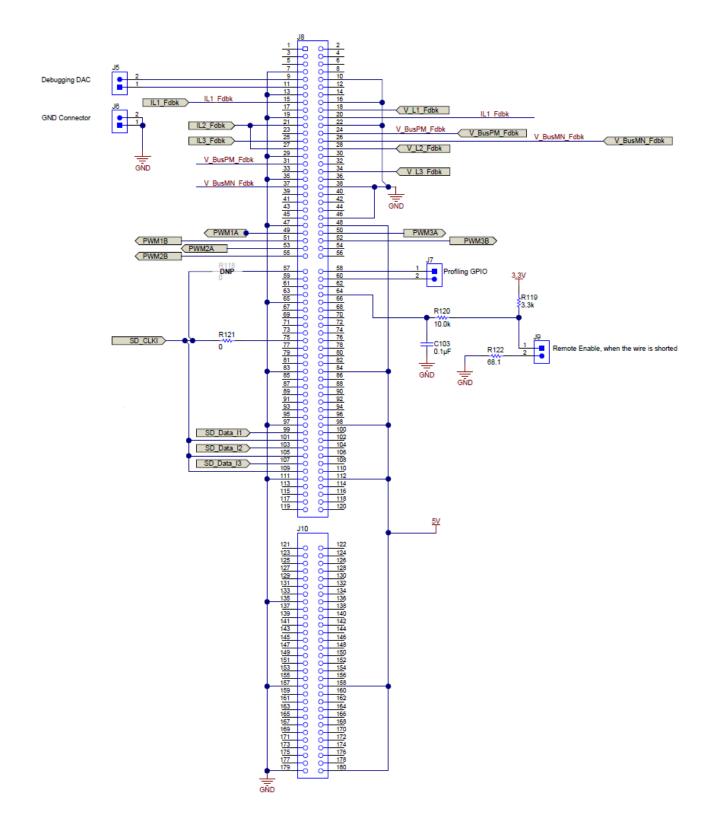

| 8.1.2. C    | ontrol Card:                                              |                |

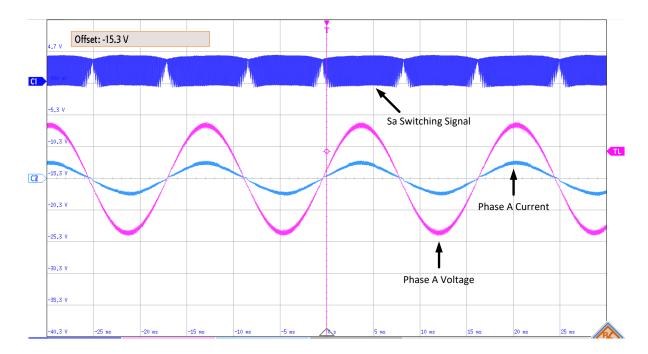

| 8.3. Exper  | rimental Results:                                         |                |

| Chapter 9.  | Conclusion and Recommendations                            | 106            |

| 9.1. Sumn   | nary:                                                     | 106            |

| 9.2. Future | e Work:                                                   | 107            |

| REFEREN     | CES                                                       |                |

| BIBLIOGR    | АРНҮ                                                      | 112            |

| APPENDICES                                    | 112 |

|-----------------------------------------------|-----|

| Appendix A: Inductance and Capacitance Design |     |

| Appendix B: MATLAB/Simulink Blocks            | 112 |

# LIST OF TABLES

| CHAPTER 2                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------|

| Table 2.1: Advantages and disadvantages of PFC rectifier       6                                                       |

| CHAPTER 3                                                                                                              |

| Table 3.1: Relation between the switching states and the switches                                                      |

| Table 3.2: Current flowing to the mid-point (i0) for each switching state                                              |

| Table 3.3: Voltage levels produced in each switching state for Sector 1                                                |

| CHAPTER 4                                                                                                              |

| Table 4.1: Relation between switching states and the switches in the conventional 3-phase         rectifier         34 |

| Table 4.2: Vectors produced by different switching states in 2-Level converters                                        |

| Table 4.3: Relation between the reference vector's angle and dwell time                                                |

| CHAPTER 5                                                                                                              |

| Table 5.1: Identification of the sectors based on the polarity of phases       40                                      |

| Table 5.2: Identification of the sectors based on the angle of the space vector                                        |

| Table 5.3: Results of switching function in each sector                                                                |

| Table 5.4: Voltage analysis in the Vienna rectifier                                                                    |

| Table 5.5: Voltage space vectors in each sector                                                                        |

| Table 5.6: Impact of each switching state on the neutral point (n)                                                     |

| CHAPTER 6                                                                                                              |

| Table 6.1: Vienna rectifier's parameters    65                                                                         |

| CHAPTER 7                                                                                                              |

| Table 7.1: System's parameters    86                                                                                   |

| CHAPTER 8                                                                                                              |

| Table 8.1: Details of the prototype's components    94                                                                 |

| Table 8.2: Prototype's parameters                 | . 95 |

|---------------------------------------------------|------|

| Table 8.3: MCU key connections and their function | . 97 |

# LIST OF FIGURES

# **CHAPTER 2**

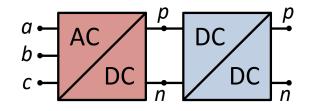

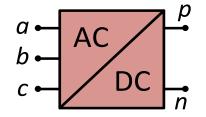

| Figure 2.1: Configuration of 2-stage PFC converters                                                  |

|------------------------------------------------------------------------------------------------------|

| Figure 2.2: Configuration of single-stage PFC converters                                             |

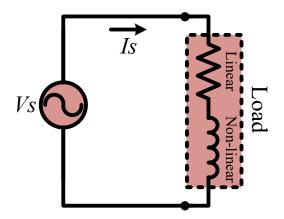

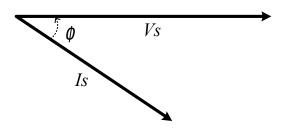

| Figure 2.3: Representation of grid-connected power electronic converters                             |

| Figure 2.4: Vector representation of the grid's voltage and current                                  |

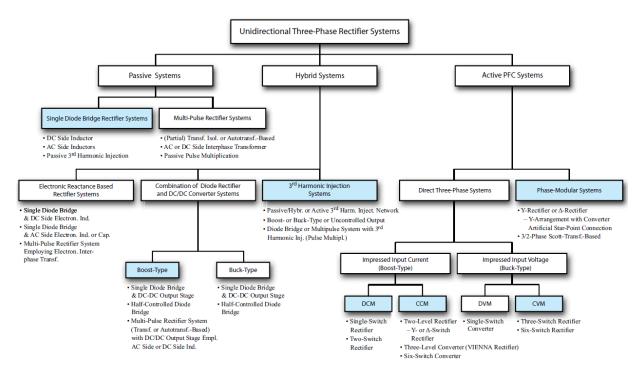

| Figure 2.5: Classification of unidirectional 3-phase rectifiers                                      |

| Figure 2.6: Configuration of the 6-switch buck rectifier9                                            |

| Figure 2.7: Configuration the Swiss rectifier10                                                      |

| Figure 2.8: Configuration of the conventional hybrid 2-stage single-phase boost rectifier 10         |

| Figure 2.9: Configuration of 3-phase boost PFC rectifier                                             |

| Figure 2.10: Configuration of 3-phase boost PFC rectifier with shifted inductors to the input        |

| Figure 2.11: Configuration of the Vienna rectifier12                                                 |

| Figure 2.12: Configuration 6-Switch boost rectifier12                                                |

| CHAPTER 3                                                                                            |

| Figure 3.1: Basic topology of the Vienna rectifier                                                   |

| Figure 3.2: Bidirectional bipolar switch                                                             |

| Figure 3.3: Current flow in the switch when the current is positive and the transistor is turned OFF |

| Figure 3.4: Current flow in the switch when the current is negative and the transistor is turned OFF |

| Figure 3.5: Current flow in the switch when the current is positive and the transistor is turned ON  |

| Figure 3.6: Current flow in the switch when the current is negative and the transistor is turned ON        | 8 |

|------------------------------------------------------------------------------------------------------------|---|

| Figure 3.7: Integrating Vienna Rectifier Circuit with the bidirectional bipolar switch                     | 9 |

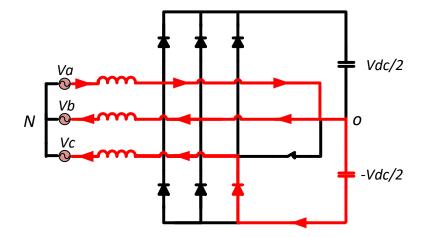

| Figure 3.8: Current flow in Vienna rectifier at "000" state for Sector 1 2                                 | 2 |

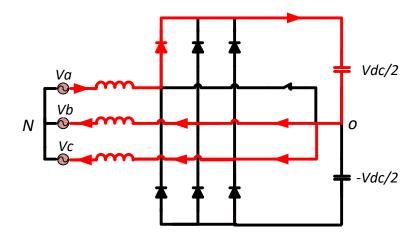

| Figure 3.9: Current flow in Vienna rectifier at "100" State for Sector 1                                   | 2 |

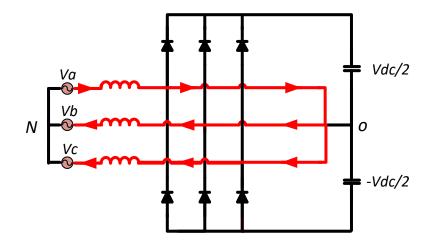

| Figure 3.10: Current flow in Vienna rectifier at "001" state for Sector 1                                  | 2 |

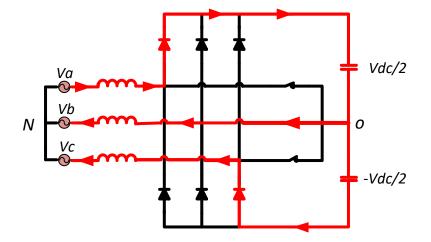

| Figure 3.11: Current flow in Vienna rectifier at "101" state for Sector 1                                  | 3 |

| Figure 3.12: Current flow in Vienna rectifier at "010" state for Sector 1 2                                | 3 |

| Figure 3.13: Current flow in Vienna rectifier at "110" state for Sector 1                                  | 3 |

| Figure 3.14: Current flow in Vienna rectifier at "011" state for Sector 1                                  | 4 |

| Figure 3.15: Current flow in Vienna rectifier at "111" state for Sector 1                                  | 4 |

| Figure 3.16: Current flow when the switching state is $(010)$ and the phase polarity is $(+)24$            | 4 |

| Figure 3.17: Current flow when the switching stat is $(010)$ and the phase polarity is $(-++)$ 2.          | 5 |

| CHAPTER 4                                                                                                  |   |

| Figure 4.1: Addition of the three vectors                                                                  | 9 |

| Figure 4.2: Space vector in $\alpha\beta$ -domain                                                          | 0 |

| Figure 4.3: Vectors in dq-coordinate                                                                       | 2 |

| Figure 4.4: Conventional 3-phase, 2-level full controlled rectifier                                        | 3 |

| Figure 4.5: Space vector diagram for 2-level converters                                                    | 5 |

| Figure 4.6: Approximating the reference space vector voltage using two active vectors and two zero vectors | 6 |

| Figure 4.7: Applying each vector for its dwell time                                                        | 7 |

| CHAPTER 5                                                                                                  |   |

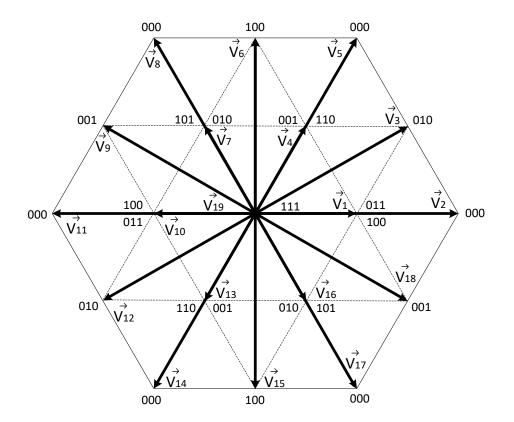

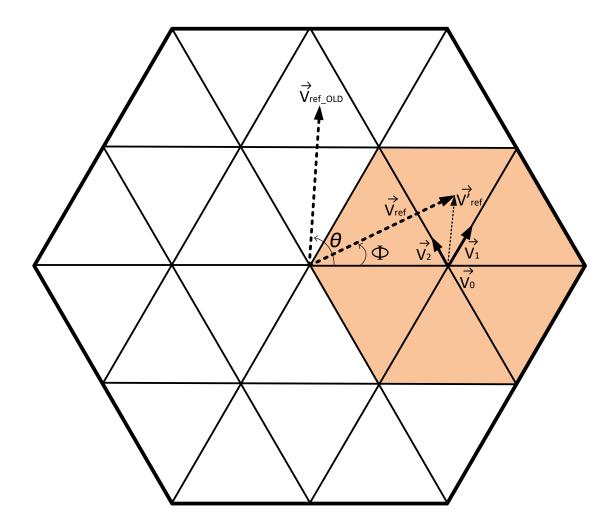

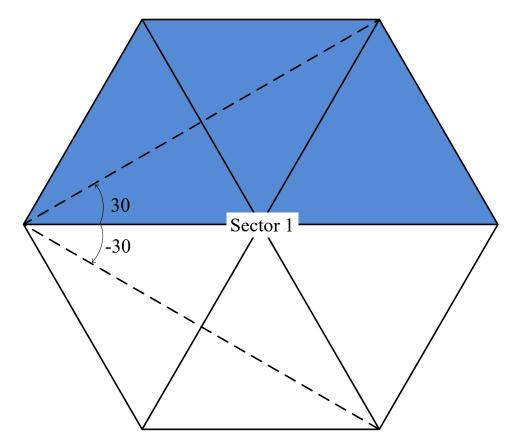

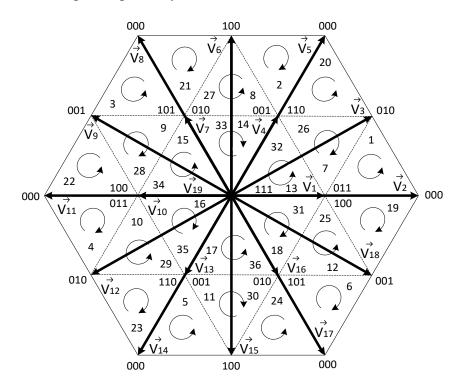

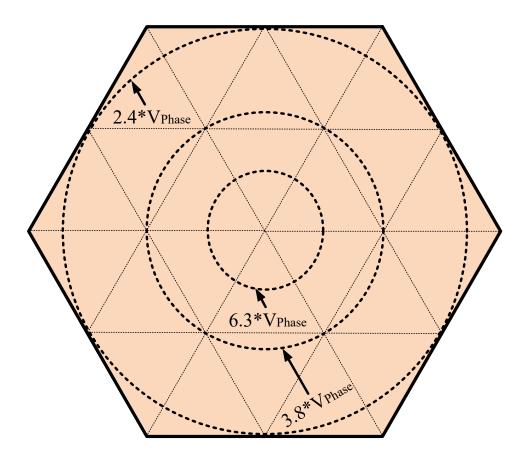

| Figure 5.1: Space vector diagram for 3-level converters                                                    | 8 |

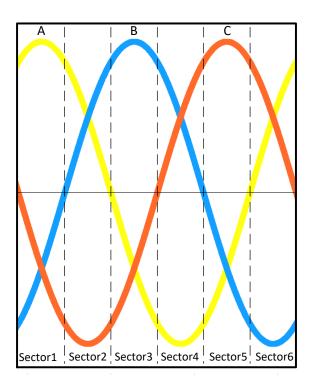

| Figure 5.2: Location of the six sectors in the 3-phase waveform                               |

|-----------------------------------------------------------------------------------------------|

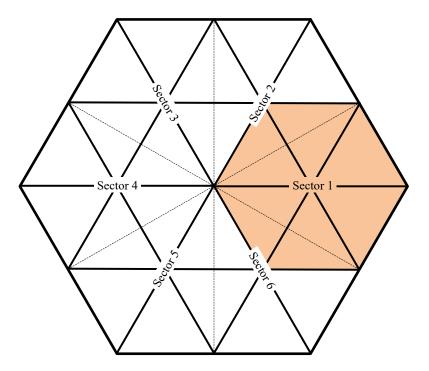

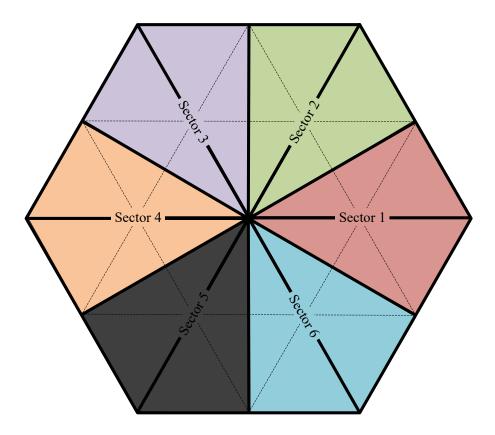

| Figure 5.3: Boundary of the sectors in the 3-level space vector diagram                       |

| Figure 5.4: Sectors in the 3-level space vector diagram                                       |

| Figure 5.5: Example of the normalized angle 51                                                |

| Figure 5.6: Zoom-in Sector 1 of the 3-level space vector diagram                              |

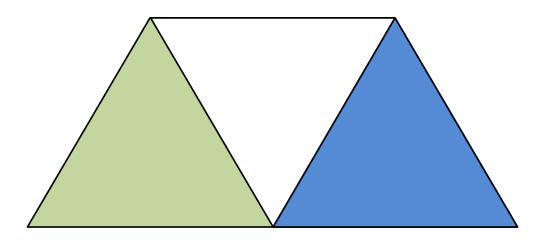

| Figure 5.7: Triangles in the upper half of Sector 1 54                                        |

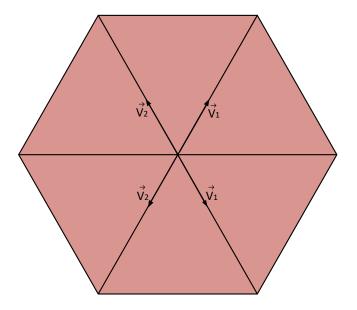

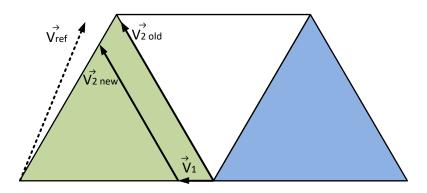

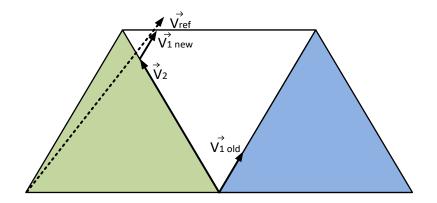

| Figure 5.8: Position of the vectors V1 and V2 when Vref falls in the first triangle           |

| Figure 5.9: Position of the vectors V1 and V2 when Vref falls in the middle triangle 56       |

| Figure 5.10: Position of vectors V1 and V2 when Vref falls in the third triangle              |

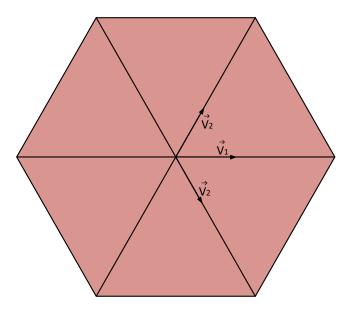

| Figure 5.11: Examples of sub-vectors shortening in the inner triangle                         |

| Figure 5.12: Examples of sub-vectors shortening in the middle triangle                        |

| Figure 5.13: Examples of sub-vectors shortening in the outter triangle                        |

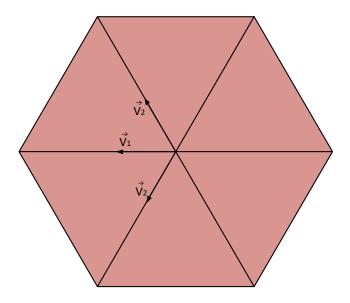

| Figure 5.14: Directions of the switching states in the 3-level SVPWM method                   |

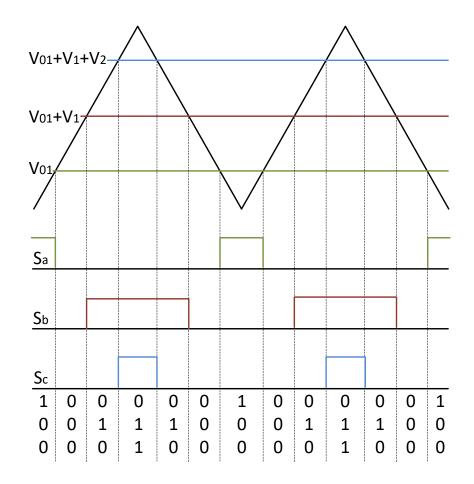

| Figure 5.15: Example of the pulse generation when the reference vector falls in triangle 1 60 |

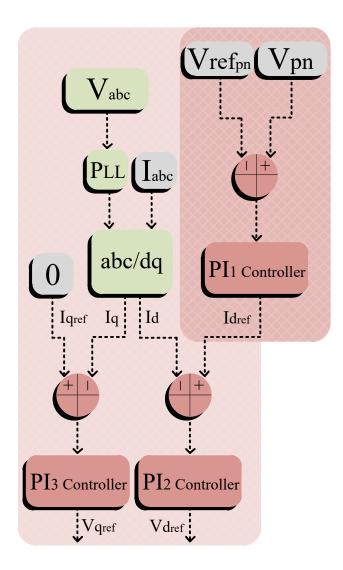

| Figure 5.16: Vienna rectifier's controller circuit                                            |

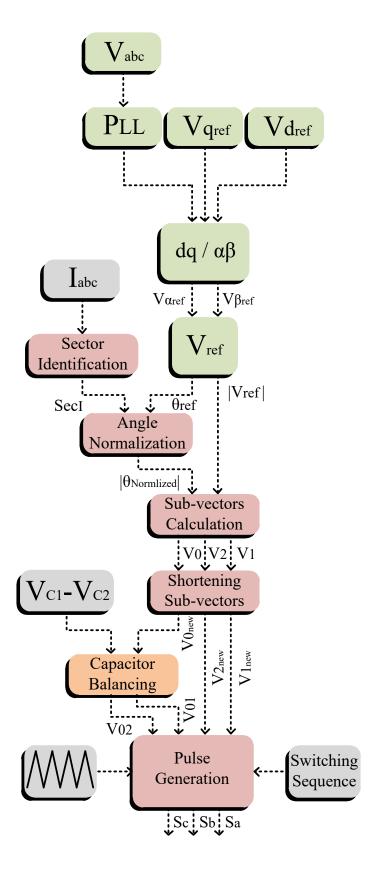

| Figure 5.17: Block diagram for the simplified SVPWM for the Vienna rectifier                  |

| CHAPTER 6                                                                                     |

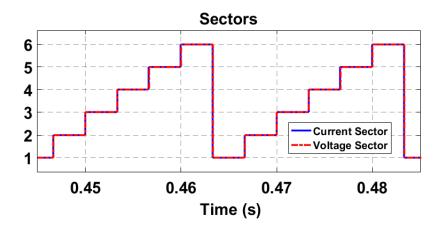

| Figure 6.1: Voltage and current sectors                                                       |

| Figure 6.2: Vienna rectifier's input current                                                  |

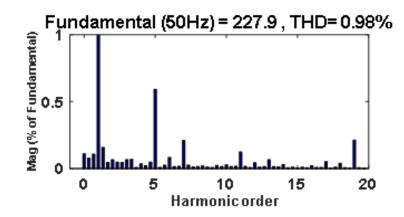

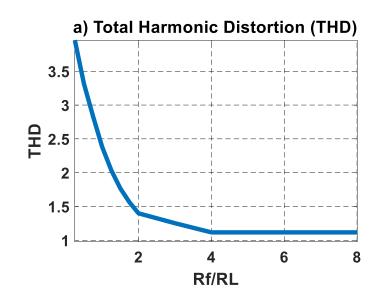

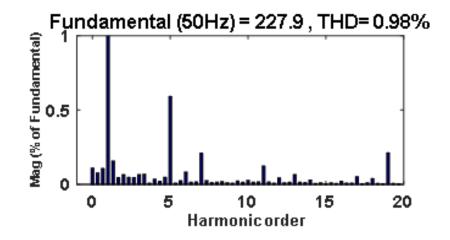

| Figure 6.3: THD of the input current                                                          |

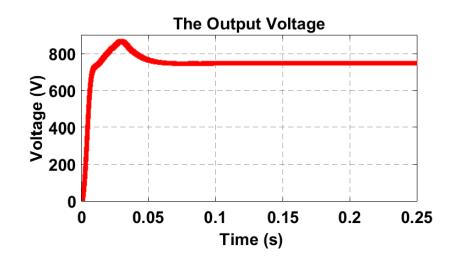

| Figure 6.4: Output voltage of the Vienna rectifier                                            |

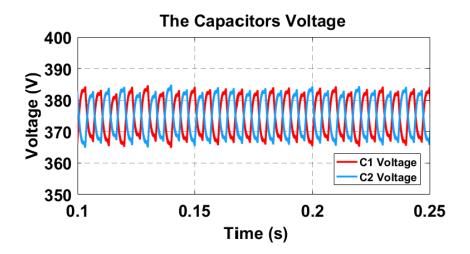

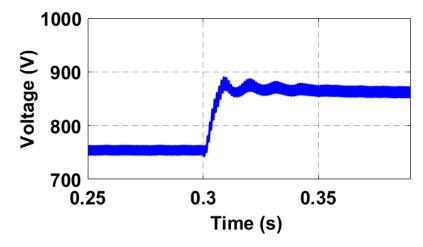

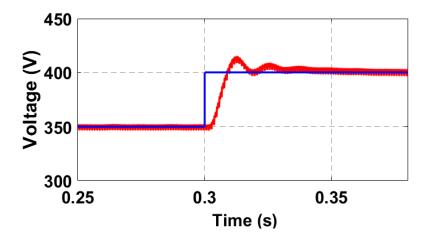

| Figure 6.5: Capacitors voltages of the Vienna rectifier                                       |

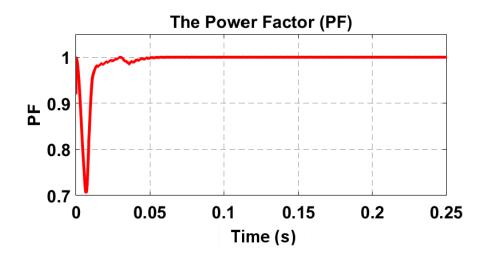

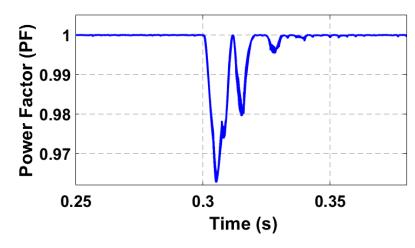

| Figure 6.6: Power factor in the Vienna rectifier                                              |

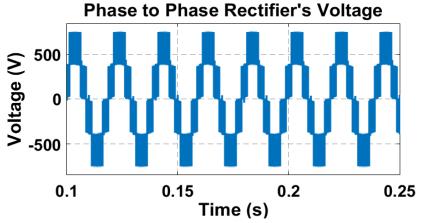

| Figure 6.7: Vienna rectifier's phase-phase voltage                                                | 9  |

|---------------------------------------------------------------------------------------------------|----|

| Figure 6.8: THD in voltage unbalance test                                                         | 9  |

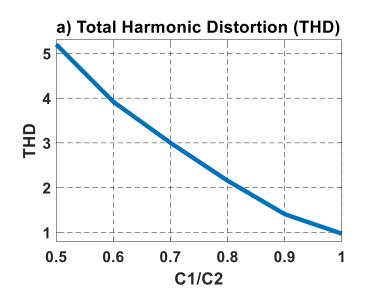

| Figure 6.9: Power factor in voltage unbalance test7                                               | 0  |

| Figure 6.10: Output voltage ripple in voltage unbalance test                                      | '1 |

| Figure 6.11: Capacitor voltages ripple in voltage unbalance test                                  | '1 |

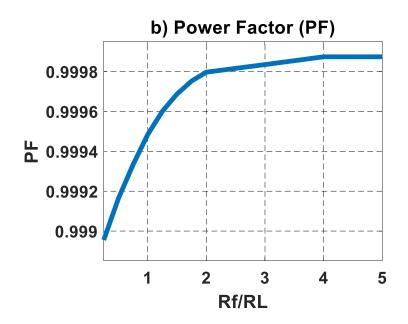

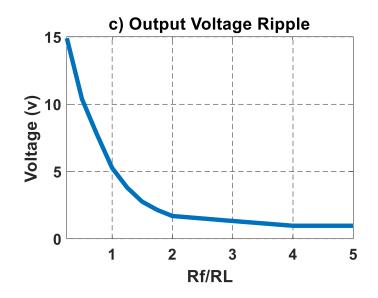

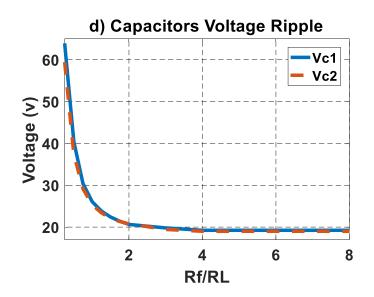

| Figure 6.12: THD in capacitor mismatch test                                                       | 2  |

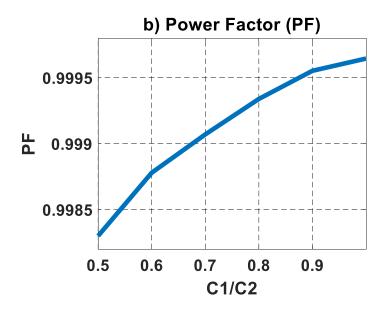

| Figure 6.13: Power factor in capacitor mismatch test7                                             | '3 |

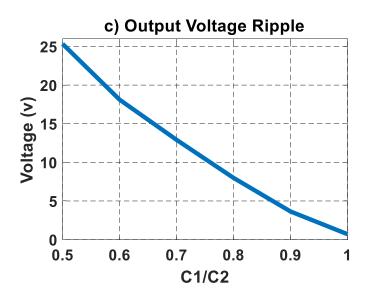

| Figure 6.14: Output voltage ripple in capacitor mismatch test                                     | '3 |

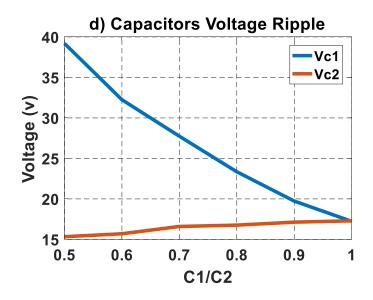

| Figure 6.15: Capacitor voltages ripple in capacitor mismatch test                                 | '4 |

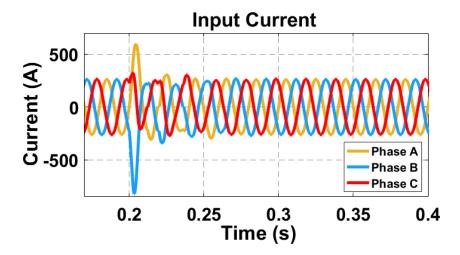

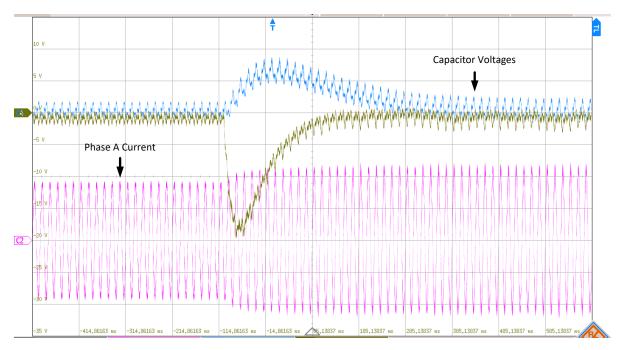

| Figure 6.16: Input current when a capacitor is short-circuited temporarly                         | '4 |

| Figure 6.17: Output voltage when a capacitor is short-circuited temporarly                        | '5 |

| Figure 6.18: Capacitor voltages when a capacitor is short-circuited temporarly7                   | 5  |

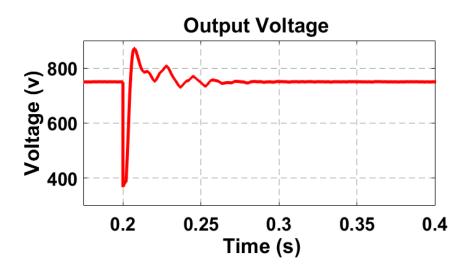

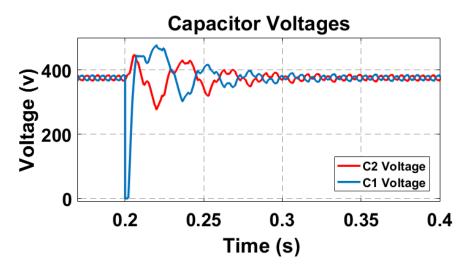

| Figure 6.19: Rectifier's input current at a sudden load change test                               | 6  |

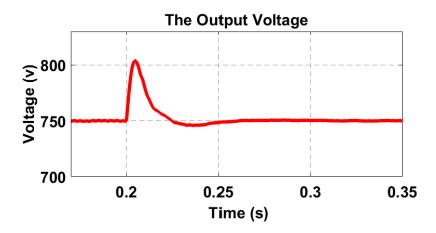

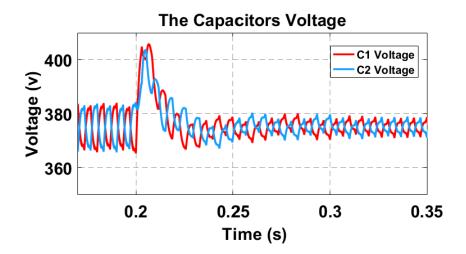

| Figure 6.20: Rectifier's output voltage at a sudden load change test                              | 7  |

| Figure 6.21: Rectifier's capacitors voltage at a sudden load change test                          | 7  |

| Figure 6.22: Relation between the Vienna rectifier's boosting ratio and SVPWM reference vector    | '8 |

| CHAPTER 7                                                                                         |    |

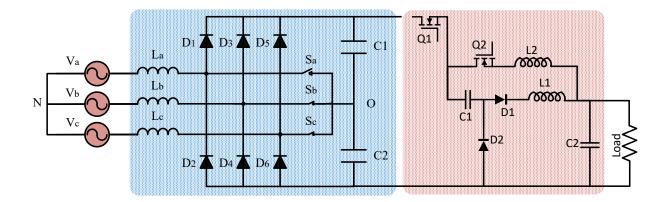

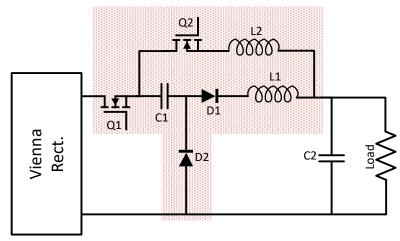

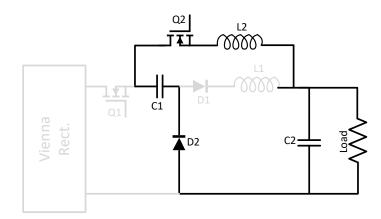

| Figure 7.1: Two stages Vienna boost rectifier and 4-switch buck converter                         | 0  |

| Figure 7.2: 4-switch Zero Currrent Switching (ZCS) buck converter with two series resonance tanks | 51 |

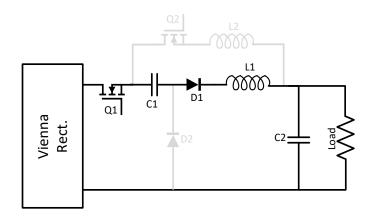

| Figure 7.3: Conduction of the 4-switch converter at the first switching interval D*Ts 8           | 2  |

| Figure 7.4: Q1 and D1 resonance current within one switching cycle Ts                             | 2  |

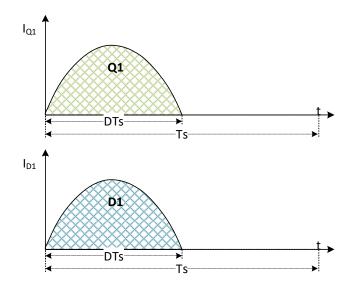

| Figure 7.5: Conduction of the 4-switch converter at the second switching interval (1-D)Ts. 8      | 3  |

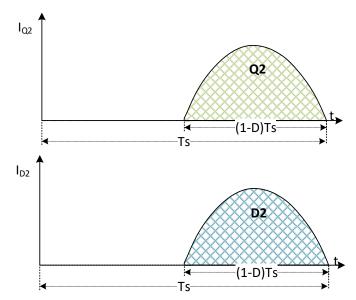

| Figure 7.6: Q2 and D2 resonance current within one switching cycle Ts                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 7.7: Capacitor C1 resonance current within one switching cycle Ts                                                                        |

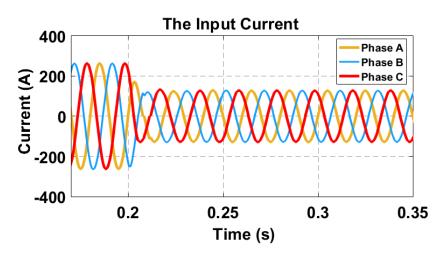

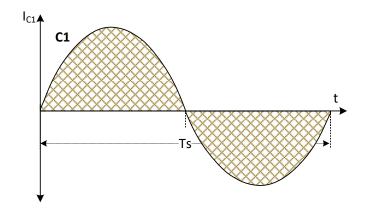

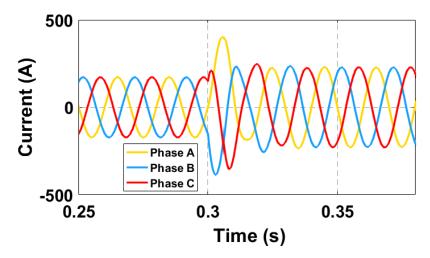

| Figure 7.8: Converter's 3-phase input current                                                                                                   |

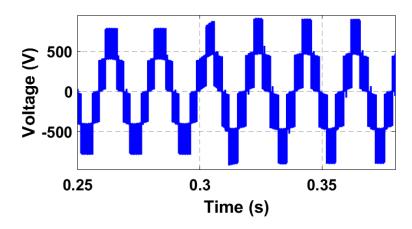

| Figure 7.9: Converter's rectified multilevel voltage                                                                                            |

| Figure 7.10: Input current THD                                                                                                                  |

| Figure 7.11: Input power factor                                                                                                                 |

| Figure 7.12: Output voltage of the Vienna rectifier ( <i>Vpn</i> )                                                                              |

| Figure 7.13: Output voltage of the second stage 4-switch converter <i>Vout</i>                                                                  |

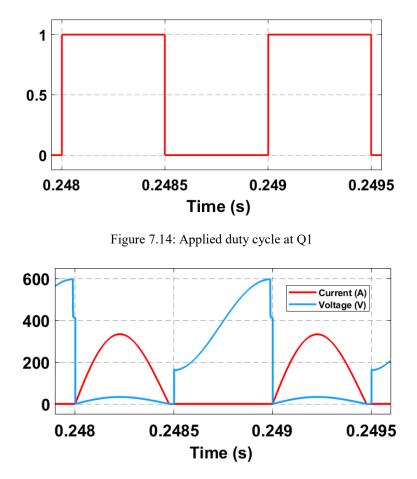

| Figure 7.14: Applied duty cycle at Q190                                                                                                         |

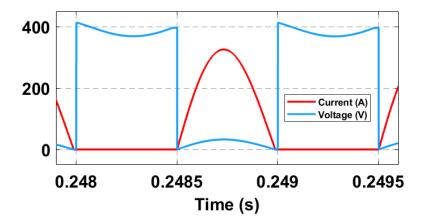

| Figure 7.15: Voltage (V) in blue across Q1 and its current (A) in red                                                                           |

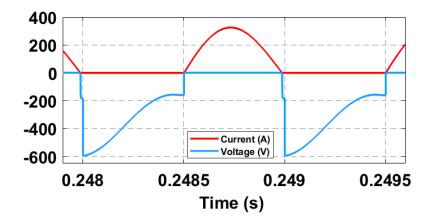

| Figure 7.16: Voltage (V) in blue across Q2 and its current (A) in red                                                                           |

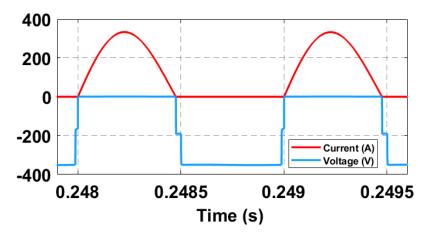

| Figure 7.17: Voltage (V) in blue across <i>D</i> 1 and its current (A) in red                                                                   |

| Figure 7.18: Voltage (V) in blue across D2 and its current (A) in red                                                                           |

| CHAPTER 8                                                                                                                                       |

| Figure 8.1: Texas Instruments Vienna rectifier Kit (TIDM-100)                                                                                   |

| Figure 8.2: Prototype's load                                                                                                                    |

| Figure 8.3: <i>C</i> 2000 <i>TM</i> F28379D microcontroller (MCU)                                                                               |

| Figure 8.4: Schematic of C2000TM F28379D microcontroller (MCU)                                                                                  |

| Figure 8.5: Experimental results for current and voltage in phase A and the switching signal to switch A                                        |

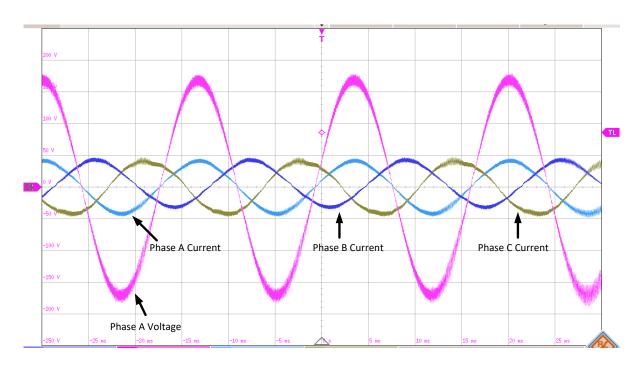

| Figure 8.6: Experimental results for the three phase currents and phase A voltage 100                                                           |

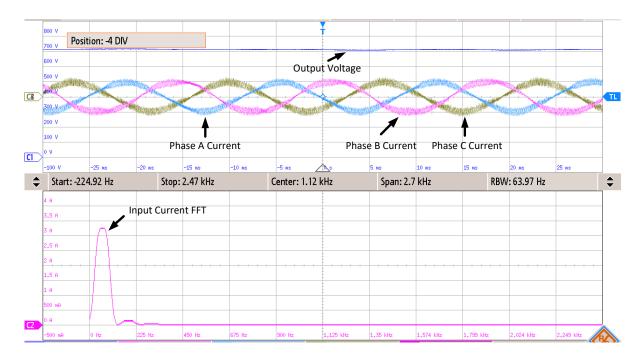

| Figure 8.7: Experimental results for the three phase currents, output DC voltage and the Fast Fourier Transformation (FFT) of the input current |

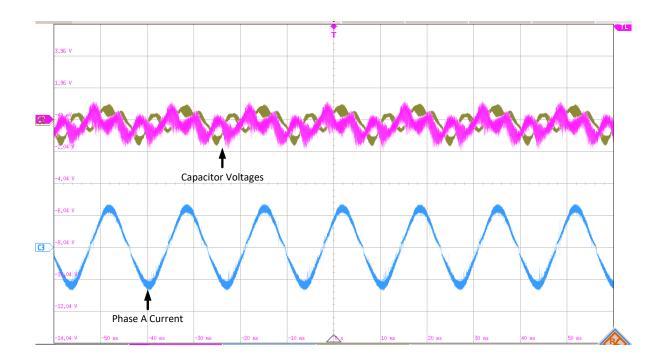

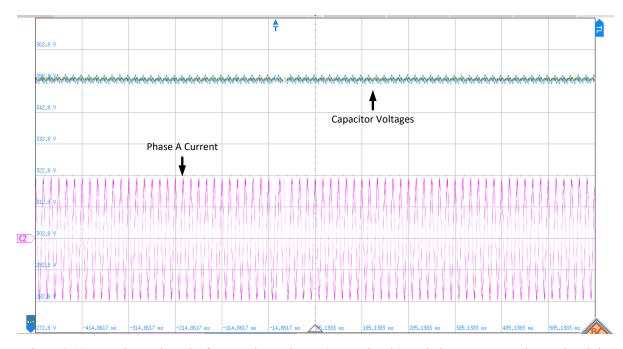

| Figure 8.8: Experimental results for current in phase A (lower signal) and capacitor voltages (upper signals)                                   |

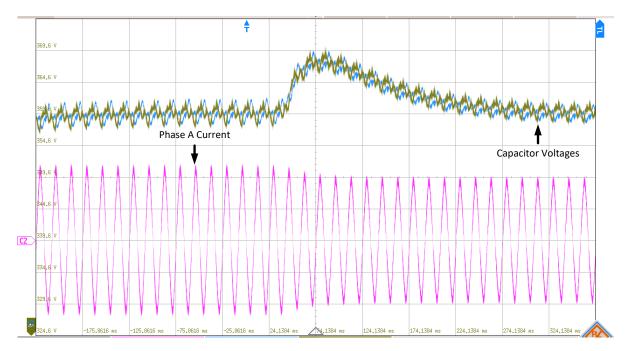

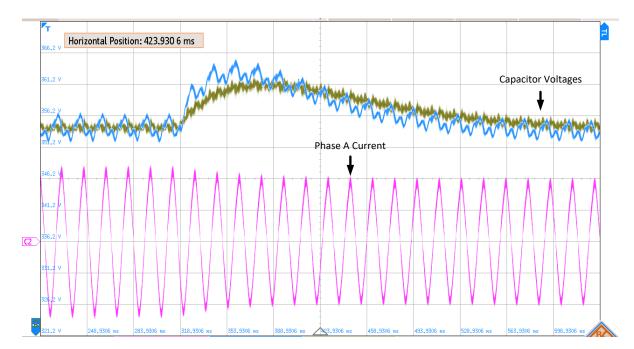

| Figure 8.9: Experimental results for capacitor voltages (upper signals) and phase A current |   |

|---------------------------------------------------------------------------------------------|---|

| (lower signal) in the test case of a load step change 102                                   | ) |

Figure 8.12: Experimental results for capacitor voltages (upper signals) and phase A current (lower signal) in the test case of the parallel fault resistor connected to capacitor C1...... 105

# **APPENDICES**

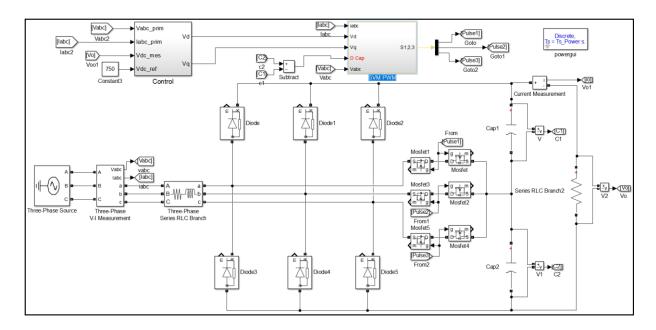

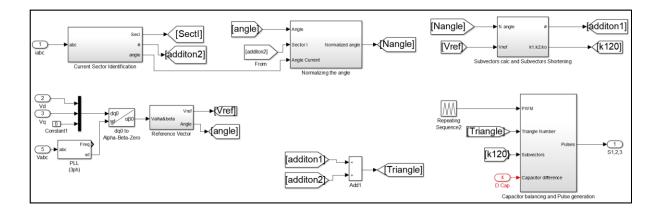

| Figure 0.1: Schematic of the overall system1                        | 12 |

|---------------------------------------------------------------------|----|

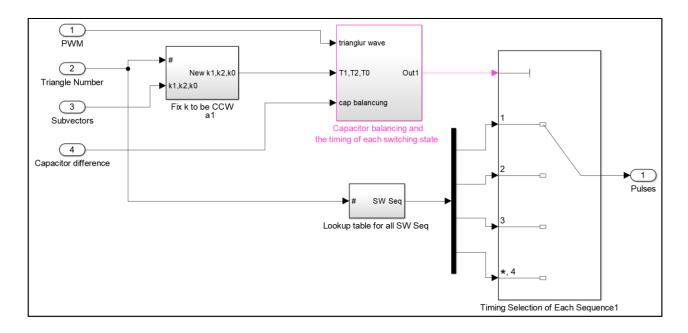

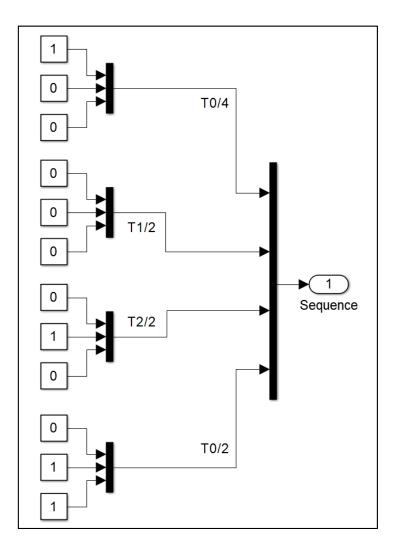

| Figure 0.2: SVPWM block 1                                           | 13 |

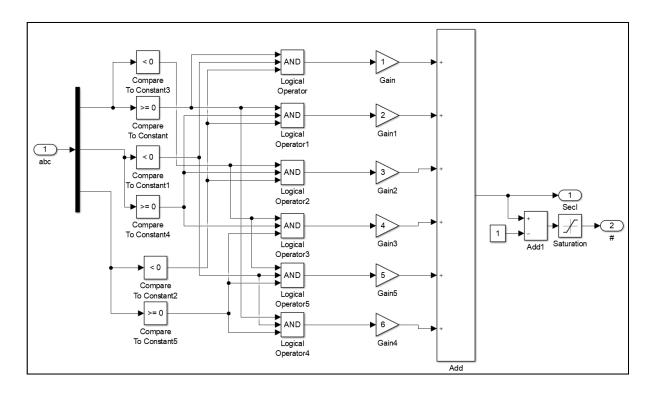

| Figure 0.3: Current Sector Identification block 1                   | 14 |

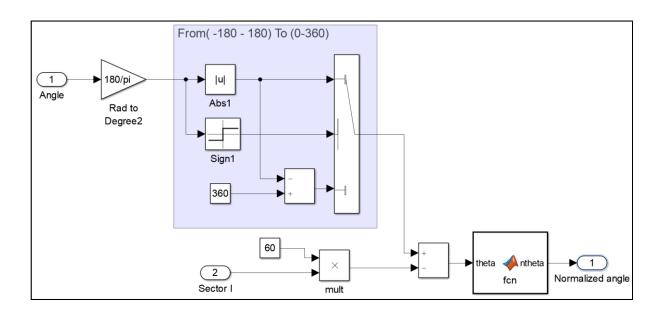

| Figure 0.4: Normalizing Angle block 1                               | 14 |

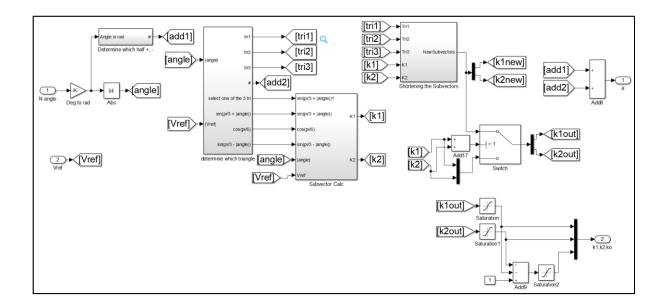

| Figure 0.5: Sub-vectors Calculation and Shortening block 1          | 15 |

| Figure 0.6: Capacitor Balancing and Pulse Generation block 1        | 16 |

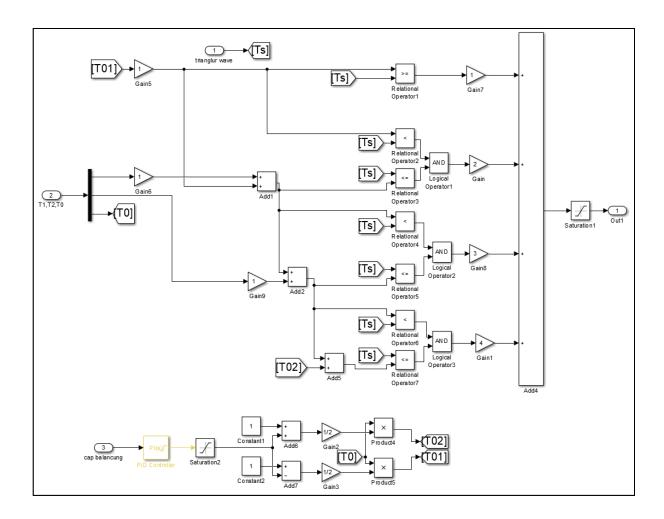

| Figure 0.7: Capacitor Balancing and Switching States Timing block 1 | 17 |

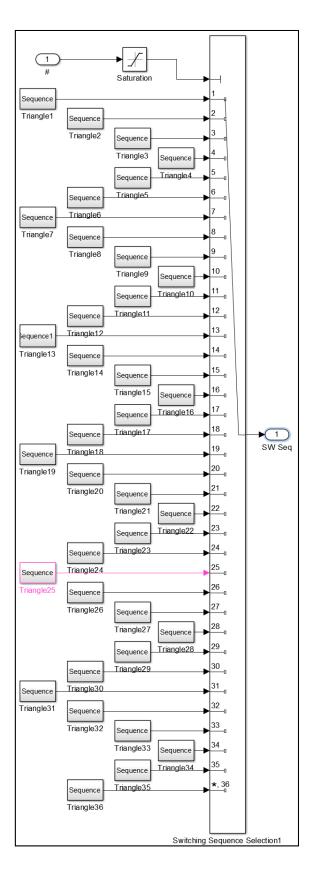

| Figure 0.8: Fixing Sub-vectors Rotation block1                      | 18 |

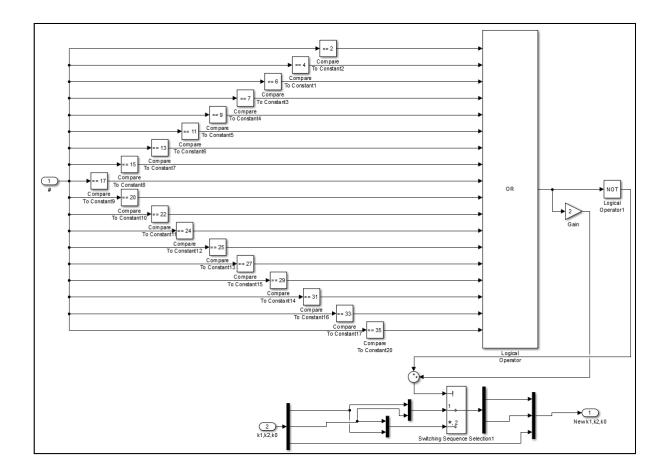

| Figure 0.9: Lookup Table for all Switching Sequences block 1        | 19 |

| Figure 0.10: Triangle 1 block1                                      | 20 |

# LIST OF ABBREVIATIONS AND SYMBOLS

| А      | Ampere                                            |

|--------|---------------------------------------------------|

| AC     | Alternative Current                               |

| ADC    | Analog-to-Digital Converter                       |

| DC     | Direct Current                                    |

| div    | Division                                          |

| EMI    | Electromagnetic Interference                      |

| EV     | Electrical Vehicle                                |

| F      | Farad                                             |

| FET    | Field-Effect Transistor                           |

| Н      | Henry                                             |

| Hz     | Hertz                                             |

| k      | Kilo                                              |

| m      | milli                                             |

| MCU    | Microcontroller Unit                              |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PF     | Power Factor                                      |

| PFC    | Power Factor Correction                           |

| PWM    | Pulse Width Modulation                            |

| R      | Resister                                          |

| S      | Second                                            |

| SD     | Secure Digital                                    |

| SVPWM  | Space Vector Pulse Width Modulation               |

| THD    | Total Harmonic Distortion                         |

| u      | micro                                             |

| UART   | Universal Asynchronous Receiver-Transmitter       |

| USB    | Universal Serial Bus                              |

| V      | Volt                                              |

| W      | Watt                                              |

| ZCS    | Zero Current Switching                            |

| Ω      | Ohms                                              |

### Chapter 1. Introduction

#### 1.1. Motivation

Most countries must find a source of renewable energy that can cover the demand increment and reduce the dependency on fossil fuel so that greenhouse gases may be reduced. The production of electricity is one of the main sources of carbon emissions which leads to global warming. To overcome this issue, the power efficiency of distribution systems must be improved. By increasing the efficiency of most commonly used Alternative Current (AC) to Direct Current (DC) rectifiers, higher power quality in distribution systems will be achieved, less energy will be consumed and less pollution will be generated at the electrical distribution systems. Electrical distribution systems supply an Alternative Current (AC) to consumers. However, increasingly a majority of the consumers' loads require a Direct Current (DC) to function; hence, AC to DC rectifiers are needed to make the utility's electricity usable for DC loads. In the last decade, much research has been done on AC to DC rectifiers but there is more to be done in this field. AC to DC rectifiers use diode-bridges to rectify the AC voltage to constant DC voltage. However, the diode-bridge draws a non-sinusoidal current with a low Power Factor (PF) which is not effective for high power applications as it reduces the efficiency and power quality. Therefore, rectifier topologies that draw high quality sinusoidal current should be used. Generally, AC to DC power rectifiers can have two, three, or more voltage levels, depending on the topology, but the complexity increases as the voltage levels increase. In addition, rectifiers can have 1-phase or 3-phase topologies. For high power application, 3phase topologies are preferred to reduce the components stress and size.

The aim of this research is to develop a Power Factor Correction (PFC) rectifier for both low and high power applications. However, it can also be applied in the first stage of a wind turbine energy system. The wind turbine generates an unusable AC voltage with a variable frequency. This AC voltage is then converted to DC voltage by the developed AC to DC rectifier. A DC to AC inverter is used to convert the voltage to a usable AC voltage with a fixed frequency. The specified objectives of this thesis are listed as follows:

- To develop a high efficient AC to DC conversion with regulated output voltage, low Total Harmonic Distortion (THD) and unity PF by using fewer active switches.

- To reduce the stress and losses of the switches that are employed in the rectifiers.

- To study the functionality of 2-level and 3-level Space Vector Pulse Width Modulation (SVPWM) method in 3-phase rectifiers.

- To reduce the complexity and computational effort of the SVPWM method.

- To analyze the Vienna rectifier using a simplified space vector method.

#### 1.3. Thesis overview

This thesis is comprised of eight chapters. In Chapter 1, an introduction to the thesis is provided, including the motivation and objectives. Chapter 2 covers the background knowledge of PFC rectifiers. It also includes the classification of these rectifiers. This chapter also provides a literature study that investigates the advantages and disadvantages of various rectifier topologies and their modulation techniques. In chapter 3, an introduction to the Vienna

rectifier is provided. The properties and operations of the Vienna rectifier is analyzed in this chapter. Chapter 4 includes a brief introduction to the 2-level SVPWM method. This chapter covers the transformation used in SVPWM methods, the available switching states, space vectors and Dwell time calculation. Chapter 5 provides a detailed space vector analysis for the Vienna rectifier. The space vectors for the Vienna rectifier is derived mathematically. Also, a detailed explanation of the simplified space vector method is illustrated. Finally, the control circuit for the Vienna rectifier is explained in this chapter. Chapter 6 illustrates MATLAB/Simulink simulation results of the Vienna rectifier using the simplified SVPWM technique. The simulation results of the system under extreme fault conditions is also illustrated in this chapter. Chapter 7 introduces an integration of the Vienna rectifier with a soft-switched buck converter to provide a high efficient system for low output voltage application. The analysis and simulation results for the proposed system are outlined in this chapter. In Chapter 8, the validity of the simplified SVPWM is checked under several fault conditions using a 2.4 kW prototype. In this chapter, the details of hardware implementation are provided. Additionally, the experimental results are illustrated and discussed. Chapter 9 provides a conclusion and discusses the potential for future work.

# Chapter 2. Background and Literature Review

- 2.1. Background

- 2.1.1. Problem statement

- 2.1.1.1. PFC Converters:

Several kinds of electronic equipment are interfaced with the supply grid. Passive loads normally draw sinusoidal current from the utility grid and they do not affect the operation of other equipment that are interfaced with the grid. However, the rapid switching of currents in power electronic devices causes harmonic distortion in the mains network. These harmonics may interfere with other electronics devices connected to the same grid. The switching behavior of power electronics devices reduces the power quality and efficiency. It causes the utility companies to supply extra power to the equipment and requires strong coupling to account for the circulating currents [1]. To overcome this issue, PFC topologies are proposed to make these switching behaviours appear as resistive loads (with a unity power factor) to the mains. The mains voltage is usually converted to a DC voltage and then adapted to the voltage needed by the load. A major drawback of the conventional PFC topologies is the inability to regulate the DC output voltage. For this reason, they are usually implemented using two stage conversions. The first stage is the diode bridge followed by a DC-link capacitor. The second stage is a DC to DC converter which takes the DC-link capacitor voltage as its input and provides a regulated DC output voltage as illustrated in Figure 2.1. However, improved PFC topologies, which have the capability to regulate the DC output voltage within one stage, do exist, as illustrated in Figure 2.2. These topologies are known as Single-stage PFC converters.

Figure 2.1: Configuration of 2-stage PFC converters

Figure 2.2: Configuration of single-stage PFC converters

The impact of the power electronic converters seen by the mains is partly described by the PF - the angle displacement between the fundamental current to voltage - and, partly by the current THD. The PF equation is derived in this section.

The grid-connected power electronic converters can be represented by the basic circuit in Figure 2.3 and the vector representation of the voltage and current is shown in Figure 2.4.

Figure 2.3: Representation of grid-connected power electronic converters

Figure 2.4: Vector representation of the grid's voltage and current

The PF can be calculated as:

Power Factor (PF) =

$$sin(\Phi) = \frac{Vs}{Is}$$

(1)

However, in the diode bridge rectifier the current waveform does not have a sinusoidal shape, which causes the PF equation to change as follows [1]:

$$PF = \frac{DPF}{\sqrt{1 + THD^2}}$$

(2)

Where DPF is displacement PF.

$$DPF = \sin(\Phi_1) = \frac{Vs}{I_{S1}}$$

<sup>(3)</sup>

where Is1 is fundamental component of the supply current,

$$PF = \frac{I_{distortion}}{I_{S1}}$$

(4)

| Table 2.1: Advantages and disadvantages of PFC rectifier [ | [1] | 1 |

|------------------------------------------------------------|-----|---|

|                                                            |     |   |

|                               | PFC Rectifiers                                             |

|-------------------------------|------------------------------------------------------------|

| Advantages                    | Disadvantages                                              |

| Better source efficiency      | Introducing greater complexity into the design.            |

| Lower power installation cost | Having more parts adversely affects reliability.           |

| Lower conducted EMI           | The generation of EMI and radio frequency interference     |

|                               | (RFI) by the active PFC circuits requires extra filtering, |

|                               | making the input filter more complex and more expensive.   |

| Reduced peak current levels   | More parts require a more costly power solution.           |

#### 2.1.2. Classification of Rectifiers:

PF circuits can be classified in two categories [1]:

- 1- Input PFC

- 2- Output PFC.

The system is categorized as input PFC when the grid is supplying a nonlinear load and the PFC circuit is placed at the input side. However, when the PFC circuit is placed between the load and the power supply, the system is called output PF. In this thesis, the input PFC system is investigated since it targets a wider range of applications.

The PFC circuits are classified into three categories based on the components as shown in Figure 2.5 and listed as follows:

#### 2.1.2.1 Passive PFC Topologies

Passive PFC circuits use passive components, such as inductors, capacitors, diodes and thyristors, to correct the displacement between the line current and the line voltage. They are purely mains commuted and do not contain any turn-off power semiconductors, which makes it impossible to regulate the output DC voltage. Examples of passive PFC circuits are given in Figure 2.5. Passive circuits are used in industry for high power applications (>100 kW) as higher current harmonics are allowed when supplying from a medium voltage mains [2].

#### 2.1.2.2 Hybrid PFC Topologies

Hybrid PFC circuits mainly consist of passive components with partial integration of active elements such as turn-off power semiconductors. In this system, a diode bridge is connected to the input side while the semiconductors switch is placed at the DC side of the rectifier. This implies that voltage regulation and sinusoidal input current is possible but they could be limited [2].

#### 2.1.2.3 Active PFC Topologies

Active PFC circuits are fully forced-commuted which use the turn-off power semiconductors in the bridge itself. They are capable of regulating the DC output voltage and shaping the input current. Since active PFC circuits are better than both passive and hybrid PFC circuits in regulating the DC voltage, they are considered in this thesis.

Figure 2.5: Classification of unidirectional 3-phase rectifiers [2]

#### 2.2. Literature Review

#### 2.2.1. Direct 3-phase PFC Rectifiers:

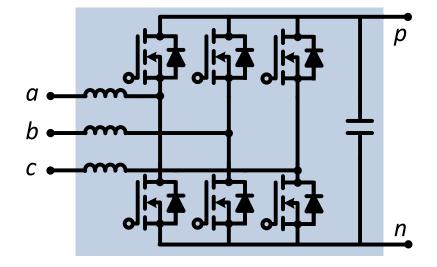

As illustrated in Figure 2.5, direct 3-phase active PFC rectifiers have two different topologies: buck and boost. In this thesis, 3-phase single-stage PFC rectifiers that provide sinusoidal input current, less than 5% THD and controlled output voltage are considered in the

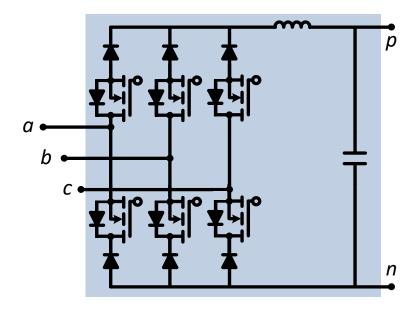

literature review. Several PFC rectifiers under these standards are provided in the literature, [3 – 6]; however, only a few are preferred in the industry, such as 6-switch buck rectifier (Figure 2.6) and SWISS rectifier (buck-type) (Figure 2.7), Vienna rectifier (boost-type), and 6-switch boost rectifier [2]. These rectifiers provide low semiconductors voltage stress, low electromagnetic interference noise, high power density, and efficiency [2]. By comparing both buck-type rectifiers, the Six-switch rectifier is preferred since its total loss is 1.2 times higher than the SWISS rectifier [7]. In addition, another reason why the topology of the SWISS rectifier is preferred is that it requires five active switches while 6-switch rectifier requires six active switches. Generally, the disadvantage of these two Buck-type rectifiers is that the input current is not directly affected by the controller [7]. In addition, the efficiency in both buck-type rectifiers is less than the boost-type rectifiers mentioned above, and they require a higher number of active and passive components. Therefore, Boost-type rectifiers are investigated in this thesis.

Figure 2.6: Configuration of the 6-switch buck rectifier

Figure 2.7: Configuration the Swiss rectifier

#### 2.2.2. 3-phase Boost PFC Rectifiers:

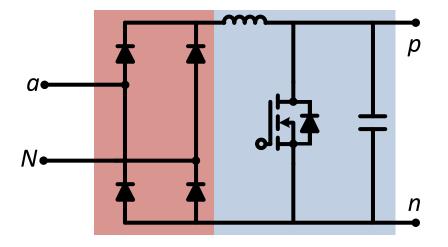

In this thesis, 3-phase, PFC, boost topologies are investigated. The idea of 3-phase boost topologies is derived from the conventional hybrid 2-stage, single-phase boost circuit shown in Figure 2.8, where the boost inductor is located at the second stage after the diode bridge and the active switch is located in parallel with the DC-link capacitor.

Figure 2.8: Configuration of the conventional hybrid 2-stage single-phase boost rectifier Similar to Figure 2.8, the topology in Figure 2.9 is extended into 3-phase, which contains a diode bridge that is connected to the rectifier input, followed by the inductor and the active

switch before the DC-link capacitor. This topology provides the ability to regulate the DC output voltage. However, the blockage nature of the diode bridge increases the current distortion (THD = 30%) [8].

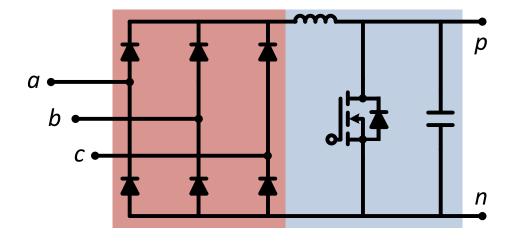

Figure 2.9: Configuration of 3-phase boost PFC rectifier

To improve the THDi in the circuit shown in Figure 2.9, the inductor filter is moved to the input of the rectifier and distributed in the phases as shown in Figure 2.10, and the mode of operation is changed to Discontinues Conduction Mode (DCM). This change leads to a better sinusoidal shape for the input current, however, a low frequency distortion still appears at low voltage transfer ratio [9].

Figure 2.10: Configuration of 3-phase boost PFC rectifier with shifted inductors to the input

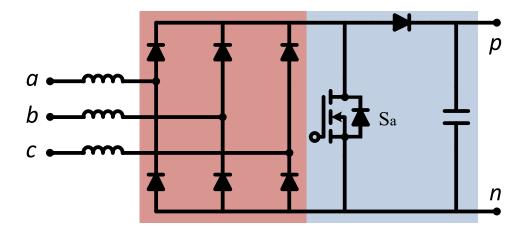

A hybrid third harmonic current injection PFC Rectifier, shown in Figure 2.10, is proposed to improve the phase current shape. The improvement is attained by introducing a new switch to control the positive and negative DC bus current. This topology results in a sinusoidal waveform for the input current [10]. In this topology, the current is injected in only one phase at the time, which is decided by the 4-quadrant switches (Sa). This is called a purely passive injection network, which requires large volume and weight. Therefore, other topologies are preferred to improve the efficiency and reduce the component sizing [2].

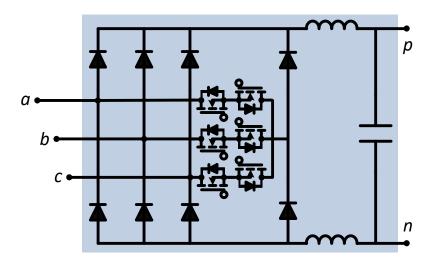

Figure 2.11: Configuration of the Vienna rectifier

Figure 2.12: Configuration 6-Switch boost rectifier

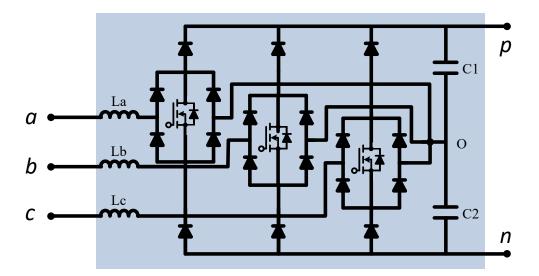

Figures 2.11 and 2.12 depict both the Vienna and 6-Switch boost rectifiers respectively. Both of these boost-type rectifiers are preferred in the industrial applications because of their high power density. However, the switching losses in the 6-Switch boost rectifier is higher than the Vienna rectifier by a factor of 2.5 and the total efficiency in Vienna rectifier is 20% higher [7]. Moreover, the inductance filter in the Vienna rectifier is half the size of the 6-Switch boost rectifier and its degree of freedom is higher since it has a 3-level characteristic [7]. One of the main advantages of the Vienna rectifier is the reduced voltage stress on the switches due to the 3-level characteristics. In addition, small boost inductors are required while sinusoidal current waveform with low THDi, high efficiency, and power density are gained. Due to these advantages, the Vienna rectifier is chosen for further investigation in this thesis.

### 2.2.3. Modulation Techniques for the Vienna Rectifier:

The 3-phase, 3-switch, 3-level Vienna rectifier is widely used in several applications, such as for telecommunication supplies and off-board Electric Vehicle (EV) charging etc. [11 - 12]. For applications in the range of several kilowatts, the Vienna rectifier is able to function well above 100 kHz switching frequency depending on electromagnetic compatibility (EMC) requirements [13]. Several researchers have employed sinusoidal Pulse Width Modulation (PWM) and hysteresis modulators to improve the performance of the Vienna rectifier, which is easily built using simple analog circuits [14 - 16]. On the other hand, these types of modulators increase the harmonics since it works in an inconstant switching frequency. To reduce the harmonics, digital controllers based on Field Programmable Gate Arrays (FPGA) and Digital Signal Processors (DSP) are used with constant switching frequency [17 - 21]. Although several modulation techniques have been applied to the Vienna rectifier, the SVPWM method has shown an excellent performance [22]. Another advantage of the SVPWM

is the ability to modify the location and timing of the pulses, which is an important factor for eliminating certain harmonics. Using SVPWM for the Vienna rectifier provides an extra advantage of balancing the DC-link's voltage by changing the time ratio of the two redundant switching states [23 - 27]. Numerous research studies have employed SVPWM for this rectifier; many studies have focused on neutral point balancing [28 - 30], where others proposed methods to improve the zero crossing distortion [31-33]. SPVPWM is also tested under unbalanced load conditions [34 - 36]. However, only limited research studies are focused on improving the main disadvantages of this modulation technique which are the high complexity and the high computational requirement such as [13], [37 - 39]. In this research, a further simplified SVPWM technique, first proposed in [40], is analysed and explained in detail. This method shows a significant reduction in the complexity and computational requirements. However, this simplified technique has not been implemented and its results have not yet been reported in the literature. Moreover, in this thesis, the modulation technique is tested under different extreme faults, such as a sudden load change, unbalanced capacitor voltages, capacitor mismatch and capacitor short-circuit, to check its capability and limitations. MATLAB/Simulink simulation results of the Vienna rectifier using the simplified SVPWM technique are provided.

# Chapter 3. The Vienna Rectifier

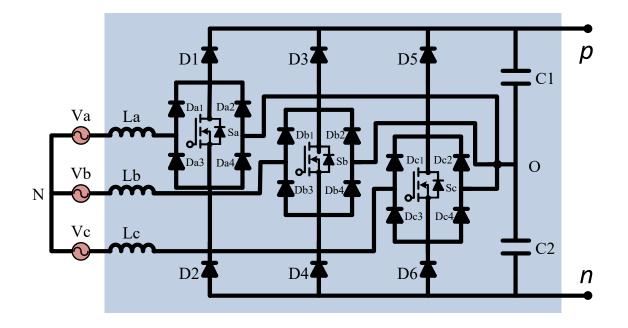

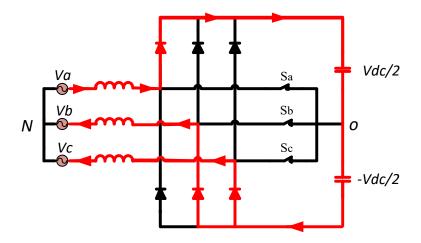

This chapter provides an introduction to the Vienna rectifier, followed by a detailed explanation of its topology and properties. The bidirectional switches used in this topology are discussed. Finally, the mode of operations and the produced voltage level are explained.

#### 3.1. Introduction to Vienna Rectifier

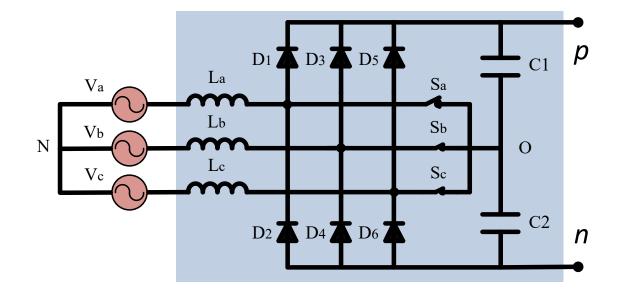

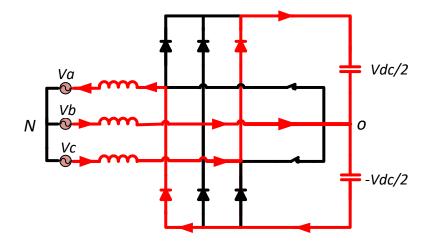

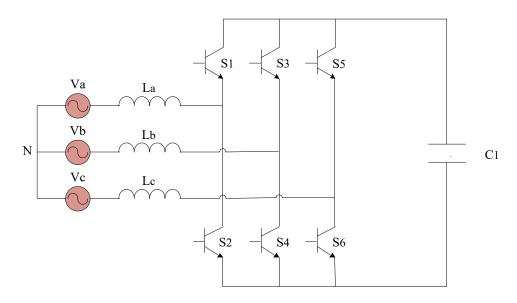

The Vienna rectifier (shown in Figure 3.1) is a 3-phase, 3-level and 3-switch (controllable) rectifier which was invented by Johann W. Kolar in 1994. It has been commonly used for several high power applications due to its high efficiency, high power density and low THD. The invention of the Vienna rectifier has reduced the number of controllable switches of 3-phase rectifiers into three switches, as opposed to the conventional rectifier, which has six switches. In this rectifier, the required AC filters are relatively small as compared to conventional rectifiers. The switching losses are minimized while the converter boost ratio is increased in this topology.

Figure 3.1: Basic topology of the Vienna rectifier

Indeed, it is well known that the main challenges in rectifiers are improving the PF and injecting sinusoidal input current. However, the Vienna rectifier has met these challenges by achieving unity PF and injecting sinusoidal input current from the mains. Moreover, the Vienna rectifier has the capability of performing well under unbalanced circumstances. In the next section, the topology of the Vienna rectifier is discussed.

#### 3.2. Vienna Rectifier Topology:

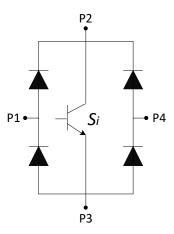

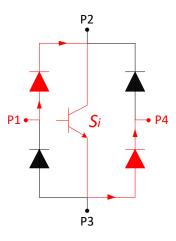

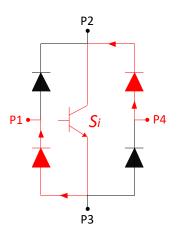

The Vienna rectifier is similar to the conventional 3-phase diode bridge rectifier, where three inductors are connected to the input of each phase. However, the output is attached to two capacitors, which are connected to a point called "capacitor midpoint (o)". The inductance filters create a current source while the capacitive filters create a voltage source. The currents produced by the inductors are injected to the capacitor midpoint through three active switches Sa, Sb and Sc. They can also charge or discharge the capacitors mid-point. Bidirectional and bipolar switches are required to fulfill the topology's requirements. As illustrated in Figure 3.2, each switch contains four diodes and a transistor to create a bidirectional switch. There are four ports in the bidirectional switch. Ports P1 and P4 are connected to the input inductance and capacitor mid-point respectively, whereas ports P2 and P4 are connected to the diodes of the rectifier's system.

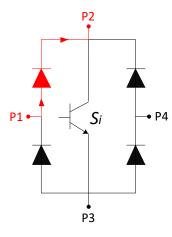

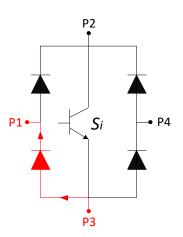

Figures 3.3 to 3.6 illustrate how the current flows in the switch. Four different paths can be taken by the currents. As shown in the Figures 3.2 to 3.6, when the transistor is OFF and the phase current is positive, the current flows from port P1 to port P3 through diode Da1. However, when the transistor is turned ON, the current flows from port P1 to port P1 to port P4 using diode Da1, transistor S and diode Da4. On the other hand, the current travels from port P3 to port P1 through diode Da3 when the current is negative and the switch is OFF. In contrast, the

current uses diode Da2, transistor S and diode Da3 to travel from port P4 to port P1 when the switch is turned ON.

Figure 3.2: Bidirectional bipolar switch

Figure 3.3: Current flow in the switch when the current is positive and the transistor is turned OFF

Figure 3.4: Current flow in the switch when the current is negative and the transistor is turned OFF

Figure 3.5: Current flow in the switch when the current is positive and the transistor is turned ON

Figure 3.6: Current flow in the switch when the current is negative and the transistor is turned ON

The switches Sa, Sb and Sc (shown in Figure 3.1) are replaced by the bidirectional bipolar switch shown in Figure 3.2. These three bidirectional bipolar switches are integrated into the diode bridge of the rectifier system. As shown in Figure 3.7, each phase in the Vienna rectifier consists of six diodes and a transistor.

Figure 3.7: Integrating Vienna Rectifier Circuit with the bidirectional bipolar switch

3.3. The Properties of the Vienna Rectifier:

## 3.3.1. The Degree of Freedom in the Vienna Rectifier

Unlike the conventional 3-phase, 2-level diode bridge rectifier, the Vienna rectifier has a limited degree of freedom as it does not have controllable switches in each phase leg. Instead, it has three switches that connect the rectifier's input to the capacitor mid-point. Moreover, turning the switches ON and OFF is not the only controlling factor in this rectifier since the direction of the phase currents decides which voltage level is applied to the rectifier (positive or negative). In other words, the position of the switches and the current directions are the two controlling factors in the Vienna rectifier.

## 3.3.2. The Operation of the Vienna Rectifier

Since the Vienna rectifier is a 3-switch rectifier, it has eight possible switching states. However, as a 3-phase system, there are six possible sectors based on the polarity of the grid as follows: Sector 1: Current in phase A is positive, while in phases B and C, they are negative (+, -, -). Sector 2: Currents in phase A and B are positive, while in phase C it is negative (+, +, -). Sector 3: Currents in phases A and C are negative, while in phase B it is positive (-, +, -). Sector 4: Current in phase A is negative, while in phases B and C they are positive (-, +, +). Sector 5: Currents in phases A and B are negative, while in phase C it is positive (-, -, +). Sector 6: Currents in phases A and C are positive, while in phase B it is negative (+, -, +).

Combining the six sectors with the eight switching states produces 48 different modes of operation. However, the modes of operation are reduced to 25 since some of them are repeated in two different sectors. The operation of this topology can be explained as follows: When the active switch Sa in phase A is OFF, the phase current travels through one of the two diodes D1 or D2, depending on its polarity, and charges the two output capacitive filters. In other words, the input current of the rectifier has three paths to travel through, depending on the current direction and the active switches status. The first path is through the upper diode D1, D3 and D5, which is possible only when the phase current is positive. The phase current travels on the second path between the rectifier's inputs to the capacitor midpoint through the active switches, which is possible for both positive and negative input phase currents. The third path is possible when the input phase current is negative, where the current travels from the bottom capacitor C2 towards the input inductor through the lower diode D2, D4 and D6. Both capacitors, C1 and C2, work as two different boost circuits where the upper capacitor boosts the positive voltage while the lower capacitor boosts the negative voltage. On the other hand, the boost inductors are charged when the rectifier input is connected to the capacitor mid-point through one of the bidirectional active switches.

As mentioned earlier, there are three possible paths for the current to travel through in each phase. However, in considering the current directions in each sector, it is evident that only two paths are possible now. For instance, the current in Sector 1 can go through the upper diode (D1) or through the active switch towards the capacitor mid-point, but it cannot pass through the bottom diode (D2). The three controllable switches decide which path the currents will take. As the Vienna rectifier has three controllable switches, eight possible switching states can be applied. The switching states and their effect on the current directions are explained in detail in this chapter. Table 3.1 shows the eight switching states.

| Switching State | Switch A | Switch B | Switch C |  |  |

|-----------------|----------|----------|----------|--|--|

| 000             | OFF      | OFF      | OFF      |  |  |

| 100             | ON       | OFF      | OFF      |  |  |

| 001             | OFF      | OFF      | ON       |  |  |

| 101             | ON       | OFF      | ON       |  |  |

| 010             | OFF      | ON       | OFF      |  |  |

| 110             | ON       | ON       | OFF      |  |  |

| 011             | OFF      | ON       | ON       |  |  |

| 111             | ON       | ON       | ON       |  |  |

Table 3.1: Relation between the switching states and the switches

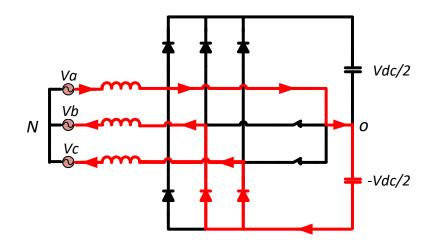

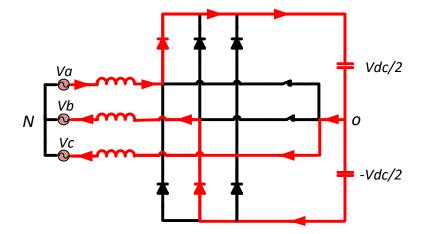

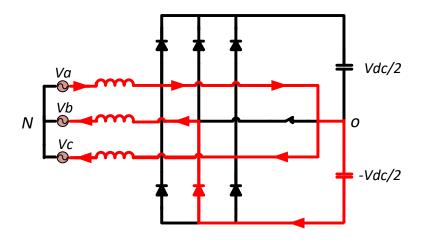

Figures 3.8 to 3.15 show the current paths when the eight switching states are applied to Sector 1 and illustrate that the current passes through the switch whenever the switch is ON. Otherwise, it travels through the upper or lower diodes, depending on the current direction of each phase. It is also observed that the lower diode in phase A and the upper diodes in phases B and C do not function in Sector 1 because phase A is positive while phases B and C are negative.

Figure 3.8: Current flow in Vienna rectifier at "000" state for Sector 1

Figure 3.9: Current flow in Vienna rectifier at "100" State for Sector 1

Figure 3.10: Current flow in Vienna rectifier at "001" state for Sector 1

Figure 3.11: Current flow in Vienna rectifier at "101" state for Sector 1

Figure 3.12: Current flow in Vienna rectifier at "010" state for Sector 1

Figure 3.13: Current flow in Vienna rectifier at "110" state for Sector 1

Figure 3.14: Current flow in Vienna rectifier at "011" state for Sector 1

Figure 3.15: Current flow in Vienna rectifier at "111" state for Sector 1

Figure 3.16: Current flow when the switching state is (010) and the phase polarity is (+ -)

Figure 3.17: Current flow when the switching stat is (010) and the phase polarity is (-++)

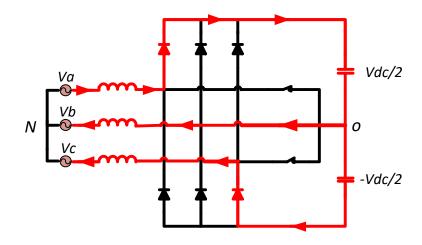

Figures 3.16 and 3.17 depict the effect when the same switching state is applied in two different sectors. Although the switching state or the switches' position for both circuits are identical, the conducting diodes are different due to the difference in the phase currents' direction. In other words, in both circuits, the switching state (010) is applied in sector (+ - -) and (- + +). The switching state (010) means the switches Sa and Sc are OFF while the switch Sb is ON. The figure illustrates how one switching state can result in different circuits and produce different voltage levels.

For several switching states, different current (io) is injected to the capacitor midpoint. The presence of io causes voltage unbalance between the two capacitors C1 and C2. It is therefore imperative that this current needs to be further analyzed. Table 3.2 shows the current io for each switching state in sector 1.

| Switching State | Current in Capacitor midpoint (io) |

|-----------------|------------------------------------|

| 000             | 0                                  |

| 100             | ia                                 |

| 001             | ic                                 |

| 101             | -ib                                |

| 010             | ib                                 |

| 110             | -ic                                |

| 011             | -ia                                |

| 111             | 0                                  |

Table 3.2: Current flowing to the mid-point (i0) for each switching state

As mentioned earlier, the Vienna rectifier is a 3-level rectifier, which means three levels of voltage can be applied to points a, b and c with respect to point (o). Table 3.3 shows the voltage levels that correspond to each switching state in Sector 1.

| Sector   | Sa | Sb | Sc | Vao                     | Vbo                     | Vco                     |

|----------|----|----|----|-------------------------|-------------------------|-------------------------|

|          | 0  | 0  | 0  | $+\frac{\text{Vdc}}{2}$ | $-\frac{\text{Vdc}}{2}$ | $-\frac{\text{Vdc}}{2}$ |

|          | 1  | 0  | 0  | 0                       | $-\frac{\text{Vdc}}{2}$ | $-\frac{Vdc}{2}$        |

|          | 0  | 0  | 1  | $+\frac{Vdc}{2}$        | $-\frac{\text{Vdc}}{2}$ | 0                       |

| Sector 1 | 1  | 0  | 1  | 0                       | $-\frac{\text{Vdc}}{2}$ | 0                       |

|          | 0  | 1  | 0  | $+\frac{Vdc}{2}$        | 0                       | $-\frac{Vdc}{2}$        |

|          | 1  | 1  | 0  | 0                       | 0                       | $-\frac{Vdc}{2}$        |

|          | 0  | 1  | 1  | $+\frac{\text{Vdc}}{2}$ | 0                       | 0                       |

|          | 1  | 1  | 1  | 0                       | 0                       | 0                       |

Table 3.3: Voltage levels produced in each switching state for Sector 1

In conclusion, the topology and various modes of operation of the Vienna rectifier are studied and explained in this chapter. In addition, the effect of switching states on the operation and the produced voltage levels is illustrated. The impact of the mid-point current is also provided in this chapter. Since Vienna rectifier's operation differs from other converters, it has special requirement for its control; therefore, SVPWM must consider this unique structure of Vienna rectifier which is illustrated in Chapter 5. Before explaining the simplified 3-level SVPWM for the Vienna rectifier, a simple 2-level SVPWM is discussed first in Chapter 4.

## Chapter 4. SVPWM for 2-level Converters

This chapter illustrates the basics of the simplest 2-level space vector modulation technique. It also explains the Clarke and Park transformations which are essential in understanding the space vector modulation method. Finally, the switching states that produce the space vectors and the Dwell time calculation are discussed.

#### 4.1. Introduction to Space Vector

SVPWM is a real-time modulation technique that can be applied to any balanced 3phase system and it is widely used for digital control of voltage source converters. The main idea of the space vector method is transforming the three phase quantities into a 2dimensional complex plane. Depending on the converter's level, specific numbers of space vector voltages can be applied to the converter. In each switching period, three of these vectors are applied to approximate the reference vector ( $V_{ref}$ ). The time duration for the three vectors must be determined. In order to transform the 3-phase quantities onto a 2-dimentional plane, the Park and Clarke transformations are used, as explained in this chapter.

## 4.1.1. Definition:

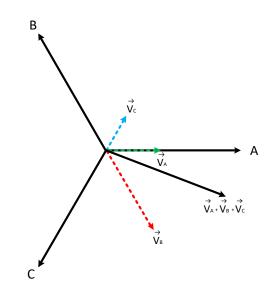

The three phase voltages can be added as a sum of vectors as shown in Figure 4.1:

$$\overrightarrow{V_{abc}} = \overrightarrow{V_a} + \overrightarrow{V_b} + \overrightarrow{V_c} = |V_a|e^{j0} + |V_b|e^{j\frac{2}{3}\pi} + |V_c|e^{-j\frac{2}{3}\pi}$$

(5)

Figure 4.1: Addition of the three vectors

Euler's formula states:  $e^{j\alpha} = \cos(\alpha) + j \sin(\alpha)$ ; hence, using Euler's formula in equation (5) results in the following equation:

$$\overrightarrow{Vabc} = |Va| - \frac{1}{2} |Vb| - \frac{1}{2} |Vc| + j \frac{\sqrt{3}}{2} |Vb| - j \frac{\sqrt{3}}{2} |Vc|$$

(6)

In order to keep the magnitude of the vectors constant during transformation, a coefficient  $\frac{2}{3}$  is multiplied to the vector  $\overrightarrow{Vabc}$ :

$$\overrightarrow{Vref} = \frac{2}{3} \ \overrightarrow{Vabc} = \frac{2}{3} \left[ |Va| - \frac{1}{2} |Vb| - \frac{1}{2} |Vc| + j \frac{\sqrt{3}}{2} |Vb| - j \frac{\sqrt{3}}{2} |Vc| \right]$$

(7)

$$\overrightarrow{V_{ref}} = \frac{2}{3} \left[ |V_a| e^{j0} + |V_b| e^{j\frac{2}{3}\pi} + |V_c| e^{-j\frac{2}{3}\pi} \right] = |V_{ref}| e^{j\theta}$$

(8)

In equation (8),  $\theta$  is the angle and V<sub>ref</sub> is the magnitude of the reference voltage vector. Equations (5) to (8) above describe the transformation from 3-phase into a 2-dimensional complex plane. However, more mathematical analysis is required to complete the transformation.

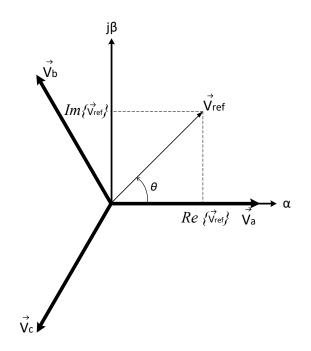

## 4.1.2. Clarke Transformation

Clarke's transformation is a mathematical transformation used to simplify the 3-phase system. It is a significant method in the space vector modulation technique which generates the reference signal. According to Euler's formula and based on equation (8):

$$\overline{V_{ref}} = |V_{ref}| \left[ \cos(\theta) + j \sin(\theta) \right]$$

<sup>(9)</sup>

In equation (9), the magnitude V<sub>ref</sub> is multiplied by real and imaginary values which can be separated as follows:

$$\mathbf{V}\alpha = Re \left\{ \overrightarrow{V_{ref}} \right\} = \frac{2}{3} \left[ |V_a| - \frac{1}{2} |V_b| - \frac{1}{2} |V_c| \right]$$

(10)

$$V\beta = Im \left\{ \overrightarrow{Vref} \right\} = \frac{2}{3} \left[ j \frac{\sqrt{3}}{2} |V_b| - j \frac{\sqrt{3}}{2} |V_c| \right]$$

(11)

Figure 4.2: Space vector in  $\alpha\beta$ -domain

As illustrated in Figure 4.2, the 3-phase system is transformed into a 2-phase system. This transformation produces a new coordinate system that is called a stator coordinate system because its coordinates are fixed; where the  $\alpha$ -axis corresponds to vector  $\overrightarrow{Va}$  and the  $\beta$ -axis is perpendicular to the  $\alpha$ -axis.

Equation (12) provides a mathematical explanation of the transformation of a 3-phase system into a 2-phase system, while equation (13) shows the conversion from a 2-phase to a 3-phase system.

$$\begin{bmatrix} V\alpha \\ V\beta \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{\sqrt{3}}{2} & \frac{-\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} Va \\ Vb \\ Vc \end{bmatrix}$$

(12)

$$\begin{bmatrix} Va \\ Vb \\ Vc \end{bmatrix} = \frac{3}{2} \begin{bmatrix} \frac{2}{3} & 0 \\ \frac{-1}{3} & \frac{1}{\sqrt{3}} \\ \frac{-1}{3} & \frac{-1}{\sqrt{3}} \end{bmatrix} \begin{bmatrix} V\alpha \\ V\beta \end{bmatrix}$$

(13)

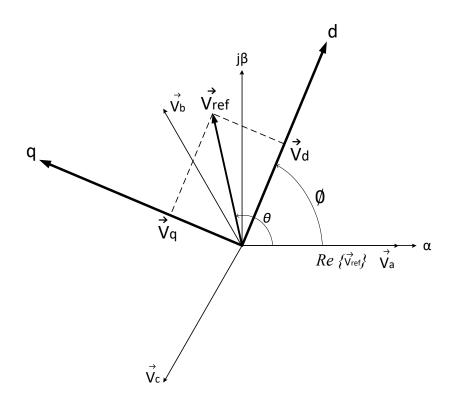

4.1.3. Park's Transformation:

Park's transformation is used to simplify complex mathematical models. It uses the stationary coordinate (Clarke's transformation) to produce a rotating coordinate system which is simpler and more useful for controlling purposes. In addition, Park's transformation allows the d-axis to rotate around a fixed coordinate system. The d-axis is shifted from the fixed axis alpha by an angle known as  $\emptyset$ , while the q-axis is perpendicular to the d-axis. Figure 4.3 illustrates Park's transformation graphically.

Figure 4.3: Vectors in dq-coordinate.

As shown in equation (13), d and q components can be found from the space vector definition:

$$\overrightarrow{V_{ref, dq}} = \frac{2}{3} \left[ |V_a| + |V_b| e^{j\frac{2}{3}\pi} + |V_c| e^{-j\frac{2}{3}\pi} \right] e^{-j(\emptyset)}$$

(14)

Using Euler's formula, the following equations are found.

$$V_d = Re \left\{ \overrightarrow{V_{ref, dq}} \right\} = |V_a|\cos(\emptyset) + |V_b|\sin(\emptyset)$$

<sup>(15)</sup>

$$V_q = Im \left\{ \overline{V_{ref, dq}} \right\} = -|V_a|\sin(\emptyset) + |V_b|\cos(\emptyset)$$

<sup>(16)</sup>

The matrix in equation (17) shows the transformation from a 3-phase system into a d-q system, which is known as Park's transformation.

$$\begin{bmatrix} d \\ q \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos(\emptyset) & \cos(\emptyset - \frac{2\pi}{3}) & \cos(\emptyset + \frac{2\pi}{3}) \\ \sin(\emptyset) & \sin(\emptyset - \frac{2\pi}{3}) & \sin(\emptyset + \frac{2\pi}{3}) \end{bmatrix} \begin{bmatrix} V_a \\ V_b \\ V_c \end{bmatrix}$$

(17)

## 4.2. Space Vector for 2-level-Converters:

### 4.2.1. Switching States:

The conventional 2-level converter has six active switches, as shown in Figure 4.4. Each phase has two controllable switches. One switch connects the phase to the positive side of the capacitor  $(+V_{dc})$ , while the other switch connects the phase to the negative side of the capacitor or to the ground (0 V). Only two voltage levels can be applied to the rectifier's input, which is why it is known as a 2-level converter. The position of each switch can be represented by two bits 0 and 1. The bit number "1" means the upper switch is turned ON while the lower switch is OFF. However, the bit number "0" means the upper switch is OFF while the lower switch is turned ON. Since there are only six switches, and the two switches in each phase cannot be both ON simultaneously, three bits are enough to represent the positions of all the switches.

Figure 4.4: Conventional 3-phase, 2-level full controlled rectifier

As shown in Table 4.1, eight different switching states can be applied to the converter. The two switching states "000" and "111" are called the zero states while the rest are called active states.

| Switching | Phase A |        | Pha    | ise B  | Phase C |        |  |

|-----------|---------|--------|--------|--------|---------|--------|--|

| State     | Upper   | Lower  | Upper  | Lower  | Upper   | Lower  |  |

|           | Switch  | Switch | Switch | Switch | Switch  | Switch |  |

| 000       | OFF     | ON     | OFF    | ON     | OFF     | ON     |  |

| 100       | ON      | OFF    | OFF    | ON     | OFF     | ON     |  |

| 001       | OFF     | ON     | OFF    | ON     | ON      | OFF    |  |

| 101       | ON      | OFF    | OFF    | ON     | ON      | OFF    |  |

| 010       | OFF     | ON     | ON     | OFF    | OFF     | ON     |  |

| 110       | ON      | OFF    | ON     | OFF    | OFF     | ON     |  |

| 011       | OFF     | ON     | ON     | OFF    | ON      | OFF    |  |

| 111       | ON      | OFF    | ON     | OFF    | ON      | OFF    |  |

Table 4.1: Relation between switching states and the switches in the conventional 3-phase rectifier

### 4.2.2. Space Vectors:

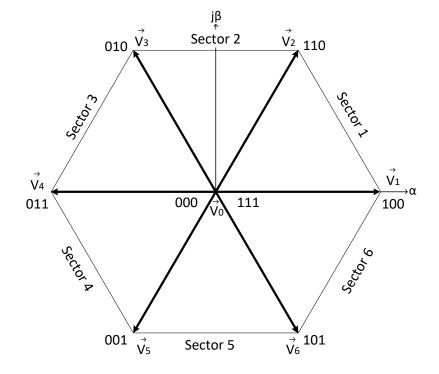

The switching states explained earlier can be represented as space vectors. Both Table 4.2 and Figure 4.5 explain the relationship between the switching states and the voltage space vector. Applying the switching states to the converter produces two zero vectors and six active vectors. The hexagon in Figure 4.5 shows the switching states as vectors where the zero vectors are located at the center of the hexogen while the active vectors are located at the edges of the hexogen. The active vectors divide the hexogen into six sectors, with each sector consisting of an equilateral triangle (all the angles are equal to 60 degrees).

| Space Vector   | Switching State | Vector Definition                    |

|----------------|-----------------|--------------------------------------|

| <b>V</b> O     | 0 0 0           | 0                                    |

|                | 111             |                                      |

| <del>V</del> 1 | 100             | $\frac{2}{3}V_d e^{j0}$              |

| V2             | 1 1 0           | $\frac{2}{3}V_d e^{j\frac{\pi}{3}}$  |

| <del>V</del> 3 | 010             | $\frac{2}{3}V_d e^{j\frac{2\pi}{3}}$ |

| V4             | 011             | $\frac{2}{3}V_d e^{j\frac{3\pi}{3}}$ |

| V5             | 0 0 1           | $\frac{2}{3}V_d e^{j\frac{4\pi}{3}}$ |

| <del>V</del> 6 | 101             | $\frac{2}{3}V_d e^{j\frac{5\pi}{3}}$ |

Table 4.2: Vectors produced by different switching states in 2-Level converters

Figure 4.5: Space vector diagram for 2-level converters

## 4.2.3. Dwell Time Calculation:

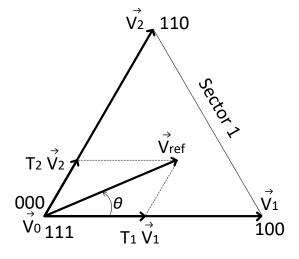

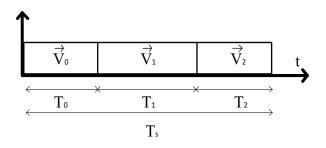

The reference vector rotates around the hexogen. In each switching period, three vectors are used for a specific period of time (Dwell time) to approximate the reference vector. The Dwell time calculation is explained in this section.

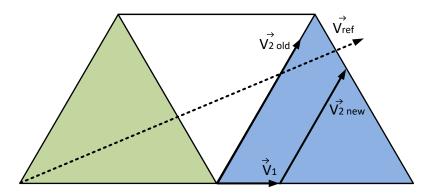

Figure 4.6 depicts an example of a reference vector  $(\overrightarrow{V_{ref}})$  that falls in sector 1 of the hexogen. The reference vector  $(\overrightarrow{V_{ref}})$  can be approximated using the three adjacent vectors  $\overrightarrow{V_1}$ ,  $\overrightarrow{V_2}$  and  $\overrightarrow{V_0}$ . Using the definition of volt-second balance, equation (18) and (19) can be derived:

$$T_s \overrightarrow{V_{ref}} = T_l \overrightarrow{V_1} + T_2 \overrightarrow{V_2} + T_0 \overrightarrow{V_0}$$

<sup>(18)</sup>

$$T_s = T_1 + T_2 + T_0 \tag{19}$$

Where  $T_1$ ,  $T_2$  and  $T_0$  are found using basic trigonometric relations, as shown in equations (20) to (22):

$$T_{I} = \frac{\sqrt{3}}{V_{dc}} T_{s} |V_{ref}| \sin(60 - \theta)$$

<sup>(20)</sup>

$$T_2 = \frac{\sqrt{3}}{V_{dc}} T_s |V_{ref}| \sin(\theta)$$

<sup>(21)</sup>

$$T_0 = T_s - (T_2 + T_1)$$

(22)

$T_1$  and  $T_2$  are the Dwell time for the vectors  $\overrightarrow{V_1}$  and  $\overrightarrow{V_2}$  respectively. Since these two vectors are stationary and cannot be changed, time division between  $\overrightarrow{V_1}$  and  $\overrightarrow{V_2}$  is used to obtain an approximated vector that is almost equal to the reference vector. In Figure 4.6, the reference vector does not touch the boundary of the hexogen. As a result, the sum of  $T_1$  and  $T_2$  is less than the switching time  $T_s$ , which means  $\overrightarrow{V_0}$  must be applied for the remaining time of the switching period ( $T_0$ ). Table 4.3 explains the relationship between the reference vector's angle and the Dwell time.

Table 4.3: Relation between the reference vector's angle and dwell time

| Reference            | 0°     | 0°< θ <30°  | 30°     | $30^{\circ} < \theta < 60^{\circ}$ | 60°    |

|----------------------|--------|-------------|---------|------------------------------------|--------|

| Angle ( $\theta^o$ ) |        |             |         |                                    |        |

| Dwell Time (s)       | T1 > 0 | T1 > T2 > 0 | T1 = T2 | T2 > T1 > 0                        | TI = 0 |

|                      | T2 = 0 |             |         |                                    | T2 > 0 |

After finding the Dwell time for each vector, the results will be combined and applied to the controllable switches. This process is repeated in each sampling time. Figure 3.7 illustrates how vectors can be combined using the calculated Dwell time.

Figure 4.7: Applying each vector for its dwell time

In conclusion, this chapter discusses the basic idea of the 2-level SVPWM. In addition, Clarke and Park transformations are explained in this chapter and space vectors for 2-level converters are derived. Finally, the procedure of synthesizing the reference vector by the adjacent vectors is illustrated. The next chapter illustrates the 3-level SVPWM for the Vienna rectifier.

# Chapter 5. Modulation and Control of The Vienna Rectifier Using Simplified 3-level SVPWM